## iND83201 "BON "

indie's highly integrated, high power supply microcontroller with high power I/Os

10/13/16

**Preliminary Data sheet**

## **1.0 TABLE OF CONTENT**

| 1.0                                                  | TABLE OF CONTENT                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0                                                  | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.0                                                  | LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.0                                                  | REGISTER CONVENTION                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.0                                                  | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.0                                                  | PINOUT AND PACKAGE                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.1                                                  | Package overview                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.2                                                  | Package dimensions9                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.3                                                  | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.0                                                  | ELECTRICAL CHARACTERISTICS 12                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.1                                                  | Absolute maximum Rating12                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.1<br>7.2                                           | Recommended Operating Conditions12                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                      | •                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7.2                                                  | Recommended Operating Conditions12                                                                                                                                                                                                                                                                                                                                                                                           |

| 7.2<br>7.3                                           | Recommended Operating Conditions       12         Current Consumption       13         DEVICE OVERVIEW       14         Microcontroller Subsystem       15         .1 Timers (0,1, and 2)       15         .2 Watch Dog Timer       18                                                                                                                                                                                       |

| 7.2<br>7.3<br>8.0<br>8.1<br>8.1<br>8.1<br>8.1        | Recommended Operating Conditions       12         Current Consumption       13         DEVICE OVERVIEW       14         Microcontroller Subsystem       15         .1 Timers (0,1, and 2)       15         .2 Watch Dog Timer       18         .3 Interrupt Vectors       20         LIN       22                                                                                                                            |

| 7.2<br>7.3<br>8.0<br>8.1<br>8.1<br>8.1<br>8.2<br>8.2 | Recommended Operating Conditions.       12         Current Consumption       13         DEVICE OVERVIEW.       14         Microcontroller Subsystem       15         .1       Timers (0,1, and 2)       15         .2       Watch Dog Timer       18         .3       Interrupt Vectors       20         LIN       22       21         LIN Interface       22         UART       35         .1       UART Operation       35 |

| 8.4.2                | SPI Registers                              | 43  |

|----------------------|--------------------------------------------|-----|

| 8.5 l <sup>2</sup> C | Interface                                  | 46  |

| 8.5.1                | I2C Functionality                          |     |

| 8.5.2                | I2C Registers                              |     |

| 0.3.2                |                                            |     |

| 8.6 AD               | С                                          | 60  |

| 8.6.1                | ADC Description                            | 60  |

| 8.1.1                | ADC Registers                              | 65  |

| 8.7 Pu               | se Width Modulators (PWM)                  | 69  |

| 8.7.1                |                                            |     |

| 8.7.2                |                                            |     |

| 0.7.2                |                                            |     |

| 8.8 GP               | IOs                                        | 74  |

|                      | GPIO Registers                             |     |

| 8.9 Sh               | ort Circuit Protection Circuits            | 100 |

| 8.9.1                | Fuse Elimination Usage Description         |     |

| 8.9.2                | Short Circuit Protection Usage Description |     |

| 8.9.3                | Short Circuit Protected Related Registers  |     |

| 0.9.5                |                                            |     |

| 8.10 C               | ock Sources                                |     |

| 8.10.1               | Clock Sources Characteristics              |     |

| 8.10.2               | Clock Related Registers                    |     |

| 8.10.3               | Clock Sources Usage Description            |     |

| 8.10.4               | Power Management Unit (PMU)                |     |

| 8.10.5               | PMU Registers                              |     |

| 8.10.6               | PMU Usage Description                      |     |

| 8.11 W               | ake-Up Timer                               | 111 |

| 9.0 RI               | EVISION HISTORY                            | 112 |

| 10.0 C               | CONTACTS                                   | 112 |

## 2.0 LIST OF TABLES

| Table 1 : PIn List                                                                                      | 10  |

|---------------------------------------------------------------------------------------------------------|-----|

| Table 2 : Absolute Maximum Ratings                                                                      | 12  |

| Table 3 : Recommended Operating Conditions                                                              | 12  |

| Table 4 : Current Consumption                                                                           | 13  |

| Table 5 : Interrupt Vector Table                                                                        | 20  |

| Table 6 - ID bits and number of bits                                                                    | 22  |

| Table 7 - LIN Inactivity Time                                                                           | 23  |

| Table 8 - LIN Wake-Up Repeat Time                                                                       | 23  |

| Table 9 - LIN Timing Related Registers                                                                  | 23  |

| Table 10 - LIN Timing Related Registers                                                                 | 24  |

| Table 11- LIN data length (when the length bits have the value "1111b")                                 | 32  |

| Table 12 - UART baud rates, divider values and errors                                                   | 36  |

| Table 13 : SPI interface signals                                                                        | 41  |

| Table 14 - Filter Tabs and output                                                                       | 58  |

| Table 15 : ADC Performance Specification, Recommended Operating Conditions, unless otherwise specified  | 60  |

| Table 16 PWM Prescaler Divide Values                                                                    | 69  |

| Table 17 -GPIO Characteristics, Typical Operating Conditions                                            | 74  |

| Table 18 - GIO and SIO Pin Functional Configuration                                                     | 76  |

| Table 19 - Clock Performance Specification, recommended operating conditions unless otherwise specified | 103 |

| Table 20 - Peripherals with specific clock source requirements                                          | 105 |

## 3.0 LIST OF FIGURES

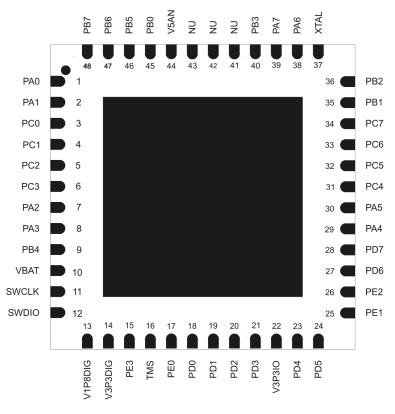

| Figure 1: Pinout Diagram (Top View)                                                       | 8  |

|-------------------------------------------------------------------------------------------|----|

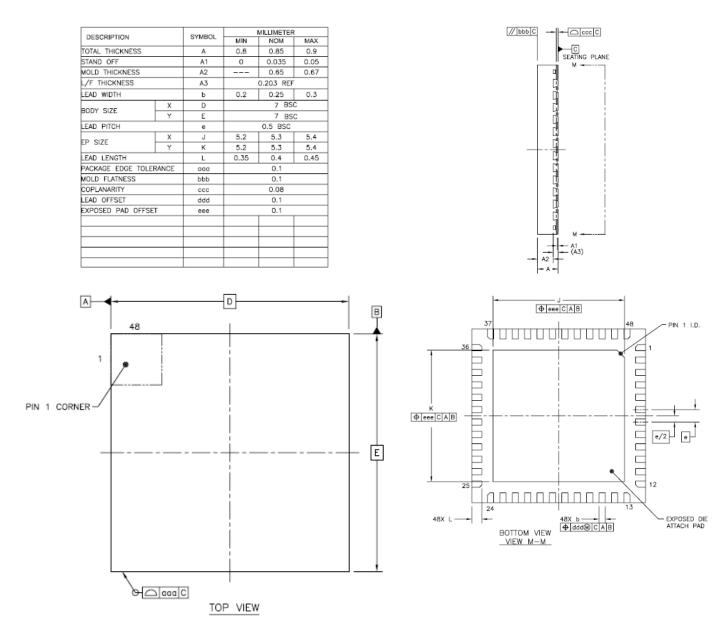

| Figure 2: QFN (7mm x 7mm) 48-pin Package Dimensions                                       | 9  |

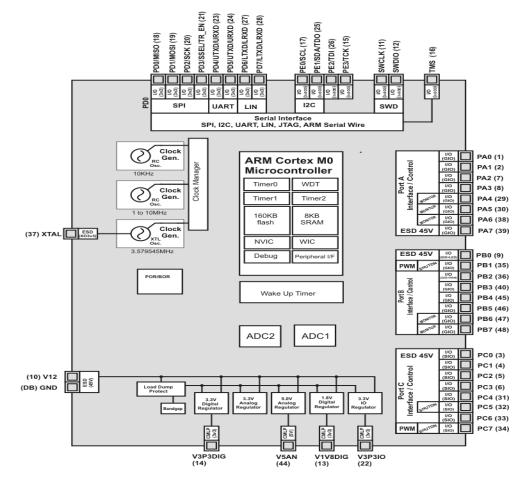

| Figure 3: BON Block Diagram                                                               | 14 |

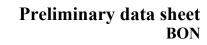

| Figure 4– SPI Timing Diagram                                                              | 42 |

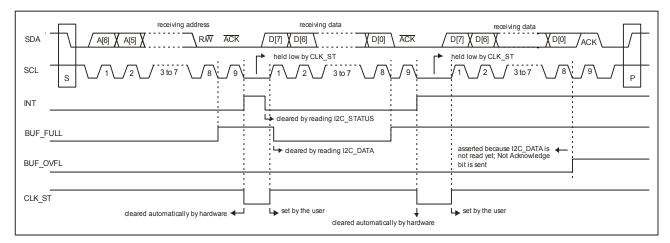

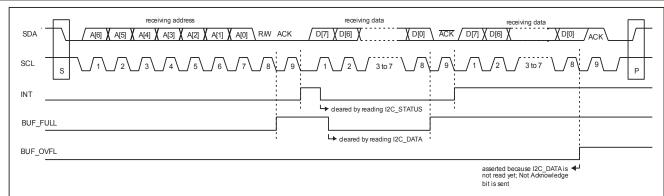

| Figure 5 – Slave Mode Timing Waveform with CLK_ST_ENB = 1 (Reception, 7-bit Address Mode) | 48 |

| Figure 6 – Slave Mode Timing Waveform with CLK_ST_ENB = 0 (Reception, 7-bit Address Mode) | 49 |

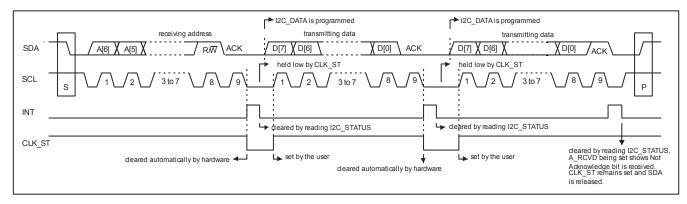

| Figure 7 – Slave Mode Timing Waveform (Transmission, 7-bit Address Mode)                  | 49 |

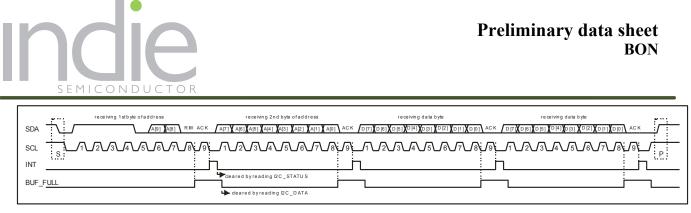

| Figure 8 – Slave Mode Timing Waveform (Reception, 10-bit Address Mode)                    | 50 |

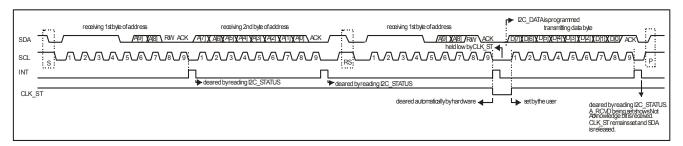

| Figure 9 – Slave Mode Timing Waveform (Transmission, 10-bit Address Mode)                 | 50 |

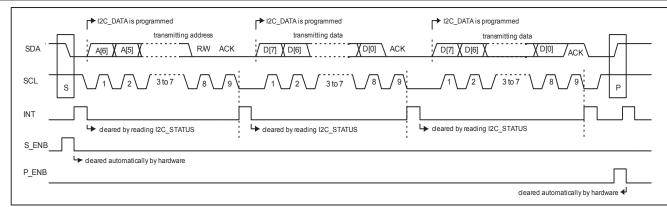

| Figure 10 – Master Timing Waveform (Transmission)                                         | 54 |

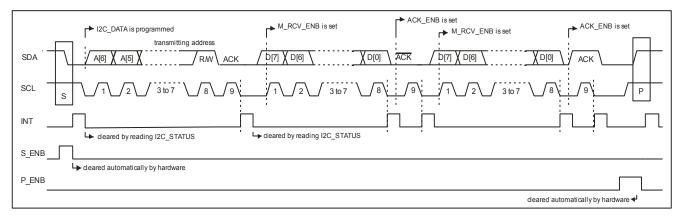

| Figure 11 – Master Timing Waveform (Reception)                                            | 55 |

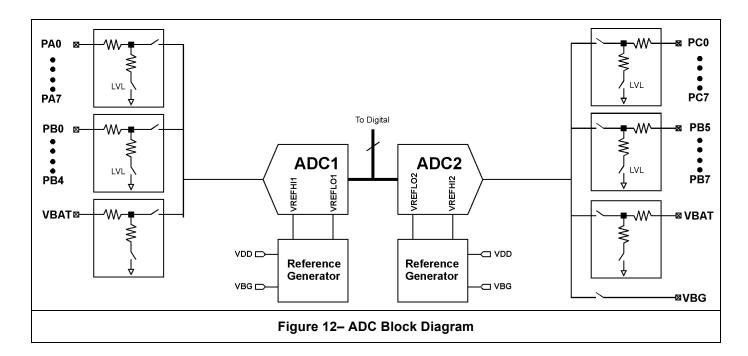

| Figure 12– ADC Block Diagram                                                              | 61 |

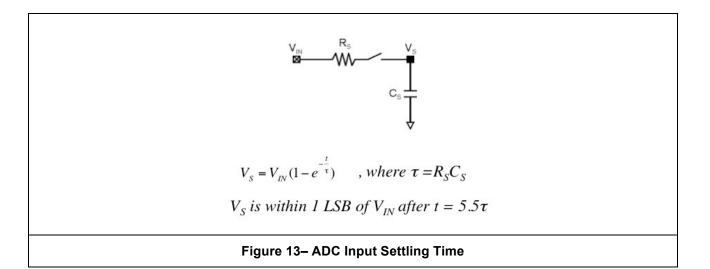

| Figure 13– ADC Input Settling Time                                                        | 62 |

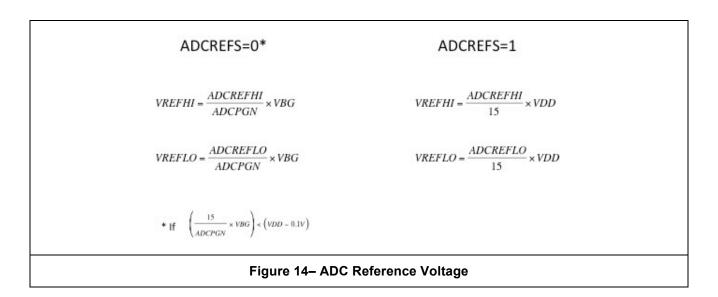

| Figure 14– ADC Reference Voltage                                                          | 63 |

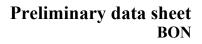

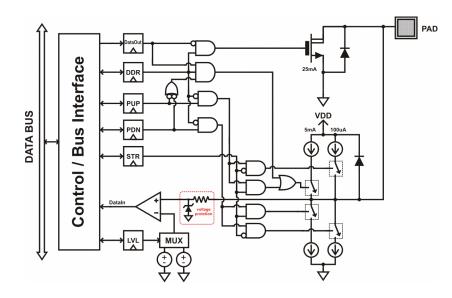

| Figure 15 - Typical GIO Interface                                                         | 76 |

| Figure 16 - Typical SIO Interface                                                         | 77 |

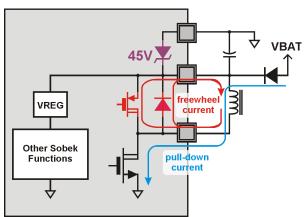

| Figure 17: Freewheel Action                                                               | 78 |

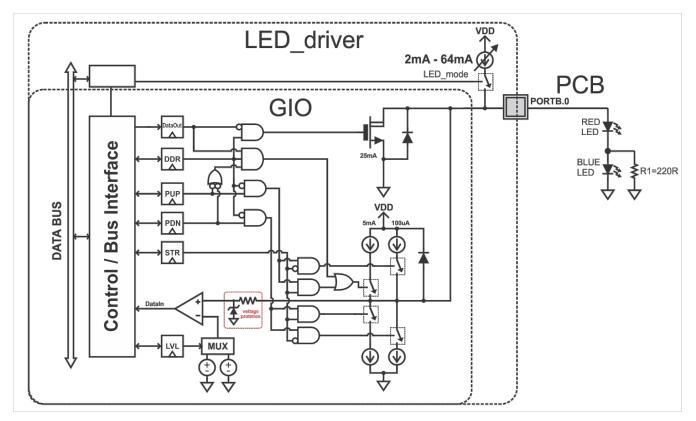

| Figure 18 – LED pin Block Diagram                                                         | 79 |

## 4.0 REGISTER CONVENTION

Several registers will be defined and explained throughout this document. The general format of the

| Name of the Register |          | Starting Address (Hex) |             |          | Reset or Default Value (Hex) |          |          |  |

|----------------------|----------|------------------------|-------------|----------|------------------------------|----------|----------|--|

| R/W                  | R/W      | R/W                    | R/W R/W R/W |          |                              | R/W      | R/W      |  |

| Bit_Name             | Bit_Name | Bit_Name               | Bit_Name    | Bit_Name | Bit_Name                     | Bit_Name | Bit_Name |  |

| MSB                  |          |                        |             |          |                              |          | LSB      |  |

description of the registers is as follows:

.

Where R/W is the read and write permissions of the specific bit.

## **5.0 GENERAL DESCRIPTION**

BON integrates an ARM Cortex-M0 low cost 32-bit microcontroller containing 160KB of flash program memory and 8KB of SRAM. It implements peripherals intended for car alarms, home alarms and garage door openers.

Main features are:

Architecture:

- ARM Cortex-M0 processor:

- Run up to 20MHz (nominal 3.58MHz Crystal)

- 10MHz Internal RC.

- o Internal 10KHz R-C low-power oscillator, for current saving operation

- System Tick Timer (SysTick 24 bits, interruptible)

- Serial Wire Debugger

- Built-in Nested Vectored Interrupt Controller (NVIC)

- Programmable Watch-Dog Timer Memory:

- 160KB of Flash Program Memory

- 8KB of SRAM

- Self-Programming

Peripherals:

- 36 General purpose I/O ports, several with Vbat and Relay Driver (200mA) capability

- Protected high current internal pull downs

- IOs with High Voltage Capability, Relay Driver Capability and selectable automatic polling mode to reduce supply current

- 2 x ADC (8-bit), total of 27 channels, and selectable input references.

- 2 x PWM (12-bit)

- LIN Interface (2.0)

- UART Interface

- SPI Interface

- I2C Interface

- LED drivers

Package: 7x7 48 pin QFN package

## 6.0 PINOUT AND PACKAGE

### 6.1 PACKAGE OVERVIEW

Figure 1: Pinout Diagram (Top View)

## 6.2 PACKAGE DIMENSIONS

The dimensions of the package are defined in the following table and drawings:

Figure 2: QFN (7mm x 7mm) 48-pin Package Dimensions

## 6.3 PIN DESCRIPTION

| Table 1 : PIn List |                   |               |                                                                                                                                     |  |  |  |

|--------------------|-------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin#               | Name              | Туре          | Description                                                                                                                         |  |  |  |

| 1                  | PA0               | GIO           | General purpose I/O operating over full Vbat range                                                                                  |  |  |  |

| 2                  | PA1               | GIO           | General purpose I/O operating over full Vbat range                                                                                  |  |  |  |

| 3                  | PC0               | SIO           | High current, general purpose I/O operating over full Vbat range                                                                    |  |  |  |

| 4                  | PC1               | SIO           | High current, general purpose I/O operating over full Vbat range                                                                    |  |  |  |

| 5                  | PC2               | SIO           | High current, general purpose I/O operating over full Vbat range                                                                    |  |  |  |

| 6                  | PC3/PWM2          | SIO           | High current, general purpose I/O operating over full Vbat range, with PWM                                                          |  |  |  |

| 7                  | PA2               | GIO           | General purpose I/O operating over full Vbat range                                                                                  |  |  |  |

| 8                  | PA3               | GIO           | General purpose I/O operating over full Vbat range                                                                                  |  |  |  |

| 9                  | PB4               | PSIO          | General purpose I/O operating over full Vbat range, with high current sourcing capability                                           |  |  |  |

| 10                 | VBAT              | Supply        | 9V to 45V battery voltage                                                                                                           |  |  |  |

| 11                 | SWCLK             | Digital Input | Serial Clock Input (Debugger)                                                                                                       |  |  |  |

| 12                 | SWDIO             | DiglO         | Serial Data (Debugger)                                                                                                              |  |  |  |

| 13                 | V1p8DIG           | Analog output | 1.8V digital voltage regulator output for external circuit and/or bypass<br>capacitor. Used internally to supply MCU and SRAM.      |  |  |  |

| 14                 | V3p3DIG (Vdd)     | Analog output | Vdd, 3.3V digital voltage regulator output for external circuit and/or bypass capacitor. Used internally to supply digital circuits |  |  |  |

| 15                 | PE3/TCK           | 3V3IO         | 3.3V I/O, or JTAG test mode clock                                                                                                   |  |  |  |

| 16                 | TMS               | 3V3IN         | JTAG test mode select                                                                                                               |  |  |  |

| 17                 | PE2/LIN_TR_EN TDI | 3V3IO         | 3.3V I/O, LIN_TR_EN or JTAG TDI                                                                                                     |  |  |  |

| 18                 | PD0/MISO          | 3V3IO         | 3.3V I/O, SPI-MISO                                                                                                                  |  |  |  |

| 19                 | PD1/MOSI          | 3V3IO         | 3.3V I/O, SPI-MOSI                                                                                                                  |  |  |  |

| 20                 | PD2/SCK           | 3V3IO         | 3.3V I/O or SPI-SCK                                                                                                                 |  |  |  |

| 21                 | PD3/SSEL          | 3V3IO         | 3.3V I/O, SPI-SSEL                                                                                                                  |  |  |  |

| 22                 | V3p3IO            | Analog output | 3.3V voltage regulator output for external circuit and/or bypass capacitor                                                          |  |  |  |

| 23                 | PD4/UTXD/URXD     | 3V3IO         | 3.3V I/O, UART-TXD or UART-RXD                                                                                                      |  |  |  |

| 24                 | PD5/UTXD/URXD     | 3V3IO         | 3.3V I/O, UART-TXD or UART-RXD                                                                                                      |  |  |  |

| 25                 | PE0/SCL           | 3V3IO         | 3.3V I/O or open drain I2C SCL                                                                                                      |  |  |  |

| 26                 | PE1/SDA/TDO       | 3V3IO         | 3.3V I/O or open drain I2C-SDA or JTAG TDO                                                                                          |  |  |  |

# Indie

| Table 1 : PIn List |               |            |                                                                                                                             |  |  |  |

|--------------------|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin#               | Name          | Туре       | Description                                                                                                                 |  |  |  |

| 27                 | PD6/LTXD/LRXD | 3V3IO      | 3.3V I/O, LIN-TXD or LIN-RXD                                                                                                |  |  |  |

| 28                 | PD7/LTXD/LRXD | 3V3IO      | 3.3V I/O, LIN-TXD or LIN-RXD                                                                                                |  |  |  |

| 29                 | PA4           | GIO        | General purpose I/O operating over full Vbat range or sensing input for short circuit protection                            |  |  |  |

| 30                 | PA5           | GIO        | General purpose I/O operating over full Vbat range or sensing input for short circuit protection                            |  |  |  |

| 31                 | PC4           | SIO        | High current, general purpose I/O operating over full Vbat range                                                            |  |  |  |

| 32                 | PC5/PWM1      | SIO        | High current, general purpose I/O operating over full Vbat range with PWM                                                   |  |  |  |

| 33                 | PC6           | SIO        | High current, general purpose I/O operating over full Vbat range                                                            |  |  |  |

| 34                 | PC7/PWM1      | SIO        | High current, general purpose I/O operating over full Vbat range with PWM                                                   |  |  |  |

| 35                 | PB1/PWM2      | GIO        | General purpose I/O operating over full Vbat range with PWM                                                                 |  |  |  |

| 36                 | PB2           | GIO        | General purpose I/O operating over full Vbat range )                                                                        |  |  |  |

| 37                 | XTAL          | Analog In  | crystal oscillator pin or internal clock input pin, requires 100nF DC block capacitor in series between the pin and crystal |  |  |  |

| 38                 | PA6           | GIO        | General purpose I/O operating over full Vbat range or sensing input for short circuit protection                            |  |  |  |

| 39                 | PA7/PWM2      | GIO        | General purpose I/O operating over full Vbat range with PWM                                                                 |  |  |  |

| 40                 | PB3           | GIO        | General purpose I/O operating over full Vbat range                                                                          |  |  |  |

| 41                 | NU            | NU         | Not Used                                                                                                                    |  |  |  |

| 42                 | NU            | NU         | Not Used                                                                                                                    |  |  |  |

| 43                 | NU            | NU         | Not Used                                                                                                                    |  |  |  |

| 44                 | V5AN          | Analog Out | 5V voltage regulator output for external circuit and/or bypass capacitor                                                    |  |  |  |

| 45                 | PB0/LED/PWM1  | GIO        | General purpose I/O operating over full Vbat range, with PWM and LED driver                                                 |  |  |  |

| 46                 | PB5/AUX4      | GIO        | General purpose I/O operating over full Vbat range                                                                          |  |  |  |

| 47                 | PB6           | GIO        | General purpose I/O operating over full Vbat range                                                                          |  |  |  |

| 48                 | PB7           | GIO        | General purpose I/O operating over full Vbat range                                                                          |  |  |  |

| TAB                | GND           | Ground     | Ground                                                                                                                      |  |  |  |

## 7.0 ELECTRICAL CHARACTERISTICS

## 7.1 ABSOLUTE MAXIMUM RATING

Absolute maximum ratings are defined in the following table. The operation of the device above these conditions may cause lasting damage and is not recommended.

| Parameter                                 | Conditions                                        | Min. | Тур. | Max.        | Unit |

|-------------------------------------------|---------------------------------------------------|------|------|-------------|------|

| Vbat voltage                              |                                                   | -0.3 |      | +50         | V    |

| High voltage digital I/O<br>input voltage | All GIO, SIO and SPIO pins<br>configured as input | -0.3 |      | Vbat+0.3    | V    |

| Low voltage digital I/O<br>input voltage  | configured as input (3V3IO), no damage            | -0.3 |      | V3p3DIG+0.3 | V    |

| 3V Analog input voltage                   | Pins, XTAL                                        | -0.3 |      | V3p3AN+0.3  | V    |

| 5V Analog input voltage                   | Pins, PON and USTX                                | -0.3 |      | V5AN+0.3    | V    |

| Operating Temp.                           | de-rated performance, full<br>functionality       | -40  |      | +85         | °C   |

| HBM (all pins)                            |                                                   | -8   |      | 8           | kV   |

| CDM (all pins)                            |                                                   | -800 |      | 800         | V    |

| MM (all pins)                             |                                                   | -400 |      | 400         | V    |

## 7.2 RECOMMENDED OPERATING CONDITIONS

| Table 3 : Recommended Operating Conditions |            |     |     |     |      |  |  |

|--------------------------------------------|------------|-----|-----|-----|------|--|--|

| Parameter                                  | Conditions | min | typ | max | unit |  |  |

| Vbat voltage                               |            | 9   | 12  | 45  | V    |  |  |

| Operating Temp.                            |            | -40 | 25  | 85  | °C   |  |  |

## 7.3 CURRENT CONSUMPTION

| Table 4 : Current Consumption |                                            |      |      |      |    |  |  |  |  |

|-------------------------------|--------------------------------------------|------|------|------|----|--|--|--|--|

| Name                          | Min.                                       | Тур. | Max. | Unit |    |  |  |  |  |

| Sleep Mode                    | All circuits disabled, Xtal enable         |      |      | 300  | μΑ |  |  |  |  |

| CPU                           | fCPU=1MHz                                  |      | 100  |      | μΑ |  |  |  |  |

| Normal operation              | CPU running, main RC as clock, CPU clock/8 |      | 1.4  |      | mA |  |  |  |  |

## 8.0 DEVICE OVERVIEW

Figure 3 depicts a high-level block diagram of the device. The device subsystems are described in the following chapters.

Figure 3: BON Block Diagram

### 8.1 MICROCONTROLLER SUBSYSTEM

The BON device includes an embedded microcontroller subsystem, which is based on the ARM Cortex M0 core. It includes a program flash memory of 160kBytes, and an SRAM of 8kBytes. It includes three 32-bit timers, plus a dedicated watchdog timer. Additionally, it includes a **N**ested **V**ector Interrupt **C**ontroller (NVIC) to scheduled hardware interrupts, and a **W**akeup Interrupt **C**ontroller (WIC), which enable the control of the various power modes.

Further information can be obtained in the AyDeeKay document <<AyDeeKay\_Core\_160\_8.pdf>>.

#### 8.1.1 Timers (0,1, and 2)

BON implements three identical timers: Timer0, Timer1 and Timer2. These timers use the system clock as clock source and once activated count up continuously. They start from the value initially loaded into the counting register (32-bit) and, if enabled, generate an interrupt upon rolling over (0xFFFFFFF  $\rightarrow$  0x00000000).

#### 8.1.1.1 Timers Registers

There are two basic registers associated with each of three timers:

| TMR0R   | EG                                                              | 0x50020000 |     |     | 0x0000000 |     |     |  |  |

|---------|-----------------------------------------------------------------|------------|-----|-----|-----------|-----|-----|--|--|

| R/W     | R/W                                                             | R/W        | R/W | R/W | R/W       | R/W | R/W |  |  |

| T7      | Т6                                                              | Τ5         | T4  | Т3  | T2        | T1  | Т0  |  |  |

| T15     | T14                                                             | T13        | T12 | T11 | T10       | Т9  | Т8  |  |  |

| T23     | T22                                                             | T21        | T20 | T19 | T18       | T17 | T16 |  |  |

| T31     | Т30                                                             | T29        | T28 | T27 | T26       | T25 | T24 |  |  |

| MSB LSB |                                                                 |            |     |     |           |     |     |  |  |

| Bit31-0 | Bit31-0 <b>T[31:0]</b> : Timer Register initial value register. |            |     |     |           |     |     |  |  |

TMR0REG: 32-bit Timer initial value register

TMR0CTRL: Timer Control

| TMR0CTRL                                                                             |          | 0x50020004 |          |          | 0x00     |          |        |  |

|--------------------------------------------------------------------------------------|----------|------------|----------|----------|----------|----------|--------|--|

| R/W                                                                                  | R/W      | R/W        | R/W      | R/W      | R/W      | R/W      | R/W    |  |

| Reserved                                                                             | Reserved | Reserved   | Reserved | Reserved | Reserved | Reserved | TSTART |  |

| MSB                                                                                  |          |            |          |          |          |          | LSB    |  |

| Bit0 <b>TSTART</b> : Timer enable bit.<br>0 = Timer not running<br>1 = Timer running |          |            |          |          |          |          |        |  |

#### TMR1REG: 32-bit Timer initial value register

| TMR1REG |                                                                 | 0x50020008 |     |     | 0x0000000 |     |     |  |

|---------|-----------------------------------------------------------------|------------|-----|-----|-----------|-----|-----|--|

| R/W     | R/W                                                             | R/W        | R/W | R/W | R/W       | R/W | R/W |  |

| Т7      | Т6                                                              | Τ5         | T4  | Т3  | T2        | T1  | Т0  |  |

| T15     | T14                                                             | T13        | T12 | T11 | T10       | Т9  | Т8  |  |

| T23     | T22                                                             | T21        | T20 | T19 | T18       | T17 | T16 |  |

| T31     | T30                                                             | T29        | T28 | T27 | T26       | T25 | T24 |  |

| MSB     |                                                                 |            |     |     |           |     | LSB |  |

| Bit31-0 | Bit31-0 <b>T[31:0]</b> : Timer Register initial value register. |            |     |     |           |     |     |  |

#### TMR1CTRL: Timer Control

| TMR1CTRL                                                                             |          | 0x5002000C |          |          | 0x00     |          |        |

|--------------------------------------------------------------------------------------|----------|------------|----------|----------|----------|----------|--------|

| R/W                                                                                  | R/W      | R/W        | R/W      | R/W      | R/W      | R/W      | R/W    |

| Reserved                                                                             | Reserved | Reserved   | Reserved | Reserved | Reserved | Reserved | TSTART |

| MSB                                                                                  |          |            |          |          |          |          | LSB    |

| Bit0 <b>TSTART</b> : Timer enable bit.<br>0 = Timer not running<br>1 = Timer running |          |            |          |          |          |          |        |

TMR2REG: 32-bit Timer initial value register

| TMR2REG |                                                                 | 0x50020010 |     |     | 0x0000000 |     |     |  |

|---------|-----------------------------------------------------------------|------------|-----|-----|-----------|-----|-----|--|

| R/W     | R/W                                                             | R/W        | R/W | R/W | R/W       | R/W | R/W |  |

| T7      | Т6                                                              | Τ5         | T4  | Т3  | T2        | T1  | Т0  |  |

| T15     | T14                                                             | T13        | T12 | T11 | T10       | Т9  | Т8  |  |

| T23     | T22                                                             | T21        | T20 | T19 | T18       | T17 | T16 |  |

| T31     | Т30                                                             | T29        | T28 | T27 | T26       | T25 | T24 |  |

| MSB     |                                                                 |            |     |     |           |     | LSB |  |

| Bit31-0 | Bit31-0 <b>T[31:0]</b> : Timer Register initial value register. |            |     |     |           |     |     |  |

#### TMR2CTRL: Timer Control

| TMR2CTRL                                                                             | 0x50020014 |          |          | 0x00     |          |          |        |

|--------------------------------------------------------------------------------------|------------|----------|----------|----------|----------|----------|--------|

| R/W                                                                                  | R/W        | R/W      | R/W      | R/W      | R/W      | R/W      | R/W    |

| Reserved                                                                             | Reserved   | Reserved | Reserved | Reserved | Reserved | Reserved | TSTART |

| MSB                                                                                  |            |          |          |          |          |          | LSB    |

| Bit0 <b>TSTART</b> : Timer enable bit.<br>0 = Timer not running<br>1 = Timer running |            |          |          |          |          |          |        |

#### 8.1.1.2 Timer Operation

The operation of the timers is quite straightforward. Load the initial counter register, enable the timer and either check (polling mode) the current value of the counter register or enable the interrupt and process it inside the interrupt service routine.

<u>Note</u>: Inside the interrupt the application code must reload the timer counting register.

#### 8.1.2 Watch Dog Timer

BON implements a WDT (**W**atch **D**og **T**imer) that can operate in one of two basic ways: Interrupt Mode: In the event of a WDT rollover an interrupt will be generated. Reset Mode: In the event of a WDT rollover the microcontroller will reset.

#### 8.1.2.1 WDT Registers

The Watch Dog Timer implements two 32-bit registers:

| WDTC                                                                                                      | TRL                                                                                                                                                                                    |                           | 0x50020018      |                   |                   | 0x000000x         |                  |         |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------|-------------------|-------------------|-------------------|------------------|---------|

| Reser                                                                                                     | ved                                                                                                                                                                                    | Reserved                  | Reserved        | R/W               | R/W               | R/W               | R/W              |         |

| -                                                                                                         |                                                                                                                                                                                        | -                         | -               | WDTPRES1          | WDTPRES0          | RSTFLAG           | RESETEN          | WDTEN   |

| -                                                                                                         |                                                                                                                                                                                        | -                         | -               | -                 | -                 | -                 | -                | -       |

| -                                                                                                         |                                                                                                                                                                                        | -                         | -               | -                 | -                 | -                 | -                | -       |

| -                                                                                                         |                                                                                                                                                                                        | -                         | -               | -                 | -                 | -                 | -                | -       |

| MS                                                                                                        | В                                                                                                                                                                                      |                           |                 |                   |                   |                   |                  | LSB     |

| Bit4-3                                                                                                    | WD1                                                                                                                                                                                    | PRES1: WD                 | TPRESO: WDT     | Prescaler:        |                   |                   |                  |         |

|                                                                                                           | 00 =                                                                                                                                                                                   | 2 <sup>13</sup> /SystemCl | ock             |                   |                   |                   |                  |         |

|                                                                                                           | 01 =                                                                                                                                                                                   | 2 <sup>19</sup> /SystemCl | ock             |                   |                   |                   |                  |         |

|                                                                                                           | 10 =                                                                                                                                                                                   | 2 <sup>22</sup> /SystemCl | ock             |                   |                   |                   |                  |         |

|                                                                                                           |                                                                                                                                                                                        | 2 <sup>32</sup> /SystemCl |                 |                   |                   |                   |                  |         |

| Bit2                                                                                                      | RST                                                                                                                                                                                    | FLAG: Reset               | Flag. This flag | g is set by the s | ystem at the ini  | tialization if th | e initialization | was     |

|                                                                                                           | caus                                                                                                                                                                                   | ed by a reset             | triggered by th | ne WDT. The bi    | t can be de-ass   | serted by the a   | application.     |         |

| Bit1                                                                                                      | RES                                                                                                                                                                                    | ETEN: Reset               | enable. If ena  | bled a WDT tim    | ne-out will force | the microcon      | troller to reset | t. This |

|                                                                                                           | bit can be asserted but it cannot be de-asserted.                                                                                                                                      |                           |                 |                   |                   |                   |                  |         |

| Bit0 <b>WDTEN</b> : WDT enable. This bit can be asserted but it cannot be de-asserted. It means that once |                                                                                                                                                                                        |                           |                 |                   |                   |                   |                  |         |

| the WDT is enabled it cannot be turned off until a Reset or Power-On Reset occurs.                        |                                                                                                                                                                                        |                           |                 |                   |                   |                   |                  |         |

|                                                                                                           | For instance, a system running from a 30MHz Crystal with WDTPRES[10] = 10 will trigger the WDT after approximately 0.14seconds if not cleared properly and in time by the application. |                           |                 |                   |                   |                   |                  |         |

#### WDTCTRL: WDT (Watch Dog Timer) Control Register. (32-bit)

WDTCLR: WDT Clear Register. (32-bit)

| WDTCLR |        |        | 0x5002001C |        | 0x000000x |        |        |

|--------|--------|--------|------------|--------|-----------|--------|--------|

| R/W    | R/W    | R/W    | R/W        | R/W    | R/W       | R/W    | R/W    |

| WCLR7  | WCLR6  | WCLR5  | WCLR4      | WCLR3  | WCLR2     | WCLR1  | WCLR0  |

| WCLR15 | WCLR14 | WCLR13 | WCLR12     | WCLR11 | WCLR10    | WCLR9  | WCLR8  |

| WCLR23 | WCLR22 | WCLR21 | WCLR20     | WCLR19 | WCLR18    | WCLR17 | WCLR16 |

| WCLR31 | WCLR30 | WCLR29 | WCLR28     | WCLR27 | WCLR26    | WCLR25 | WCLR24 |

| MSB    |        |        |            |        |           |        | LSB    |

Bit31-0 **WCLR[31:0]**: Clear Register. To clear the WDT counting the following words must be written in this order and without any other instruction between then:

0x3C570001

0x007F4AD6

**Warning:** Programming WDTCLR with other values or in the wrong order will cause the watchdog to throw an interrupt or reset the system.

#### 8.1.3 Interrupt Vectors

BON implements an interrupt vector defined in the following table:

| Table 5 : Interrupt Vector Table |        |                                                    |  |  |  |

|----------------------------------|--------|----------------------------------------------------|--|--|--|

| Cortex M0 Specific Exceptions    |        |                                                    |  |  |  |

| Name                             | Number | Comments                                           |  |  |  |

| HardFault_IRQn                   | -13    | HardFault handler*                                 |  |  |  |

| SVCall_IRQn                      | -5     | Supervisory call*                                  |  |  |  |

| PendSV_IRQn                      | -2     | Interrupt-driven request for system level service* |  |  |  |

| SysTick_IRQn                     | -1     | SysTick Timer interrupt                            |  |  |  |

|                                  | ·      | Cortex M0 Specific Exceptions                      |  |  |  |

| Name                             | Number | Comments                                           |  |  |  |

| BrownOut_IRQn                    | 0      | Brownout detection interrupt                       |  |  |  |

| ClkMon_IRQn                      | 1      | Clock monitor interrupt                            |  |  |  |

| -                                | 2      | RESERVED                                           |  |  |  |

| PIN_IRQn                         | 3      | Pin change interrupt                               |  |  |  |

| -                                | 4      | RESERVED                                           |  |  |  |

| -                                | 5      | RESERVED                                           |  |  |  |

| I2C_Collision_IRQn               | 6      | I <sup>2</sup> C Collision detection interrupt     |  |  |  |

| I2C_IRQn                         | 7      | I <sup>2</sup> C event interrupt                   |  |  |  |

| UART_IRQn                        | 8      | UART event interrupt                               |  |  |  |

| LIN_IRQn                         | 9      | LIN event interrupt                                |  |  |  |

| SPI_IRQn                         | 10     | SPI event interrupt                                |  |  |  |

| -                                | 11     | RESERVED                                           |  |  |  |

| -                                | 12     | RESERVED                                           |  |  |  |

| IRQ13_IRQn to<br>IRQ15_IRQn | 13-15 | RESERVED                 |

|-----------------------------|-------|--------------------------|

| TIMER0_IRQn                 | 16    | Timer0 interrupt         |

| TIMER1_IRQn                 | 17    | Timer1 interrupt         |

| TIMER2_IRQn                 | 18    | Timer2 interrupt         |

| WATCHDOG_IRQn               | 19    | Watchdog timer interrupt |

\*Note: For more information see *Cortex-M0 Devices* – *Generic Users Guide* (*ARM DUI 0497A (ID112109)*) at: <u>http://infocenter.arm.com/help/topic/com.arm.doc.dui0497a/DUI0497A\_cortex\_m0\_r0p0\_generic\_ug.pdf</u>

## 8.2 LIN

The BON device contains digital hardware, which implements a LIN 2.0 serial communications interface.

#### 8.2.1 LIN Interface

BON implements a LIN (Specification 2.0) interface. Its main characteristics are:

- Configurable for support of both master or slave functionality

- Programmable data rate between 1 Kbit/s and 20 Kbit/s (for master)

- Automatic bit rate detection (for slave)

#### 8.2.1.1 LIN Usage Description

BON implements a LIN (Local Interconnect Network) peripheral. This implementation is compatible with the specification 2.0 and allows for the selection of both Master and Slave modes.

#### 8.2.1.1.1 Data Length Control

The host controller has to define the length of the data field of the current LIN frame by adjusting the LINLENGTH register. If the data length bits[3:0] are loaded with the value "1111b" the length of the data field is decoded from Bit 5 and 4 of the identifier register (LINID) according to table below (e.g. compatibility to LIN specification 1.1). Otherwise the amount of data bytes can be written directly to the DATA\_LENGTH[3:0] register (supported values are 0...8).

| Table 6 - ID bits and number of bits |            |                                   |  |  |  |  |

|--------------------------------------|------------|-----------------------------------|--|--|--|--|

| ID (Bit 5)                           | ID (Bit 4) | Number of Bytes in the data field |  |  |  |  |

| 0                                    | 0          | 2                                 |  |  |  |  |

| 0                                    | 1          | 2                                 |  |  |  |  |

| 1                                    | 0          | 4                                 |  |  |  |  |

| 1                                    | 1          | 8                                 |  |  |  |  |

#### 8.2.1.1.2 Timing Settings for "Wake Up Repeat Time" and "Bus Inactivity Time"

The time for repeating of wake up because of no reaction on the bus and to go to sleep because of inactivity on the bus can be optionally written by the application in registers LINTIMING:

| Table 7 - LIN Inactivity Time |                            |  |  |  |  |

|-------------------------------|----------------------------|--|--|--|--|

| LINIT[1:0]                    | LIN Inactivity Time (sec.) |  |  |  |  |

| 00                            | 4                          |  |  |  |  |

| 01                            | 6                          |  |  |  |  |

| 10                            | 8                          |  |  |  |  |

| 11                            | 10                         |  |  |  |  |

| 10                            | 8<br>10                    |  |  |  |  |

| Table 8 - LIN Wake-Up Repeat Time                |     |  |  |  |  |

|--------------------------------------------------|-----|--|--|--|--|

| LINWPR1 [1:0] LIN Wake-Up Repeat<br>Time (msec.) |     |  |  |  |  |

| 00                                               | 180 |  |  |  |  |

| 01                                               | 200 |  |  |  |  |

| 10                                               | 220 |  |  |  |  |

| 11                                               | 240 |  |  |  |  |

#### 8.2.1.1.3 Bit Time Settings

The Bit rate of the LIN system has to be defined in the bit timing registers (LINBITDIV and LINBITMUL). The table below shows an overview of the registers.

| Table 9 - LIN Timing Related Registers |                                               |             |  |  |  |

|----------------------------------------|-----------------------------------------------|-------------|--|--|--|

| Name                                   | Description                                   | Width(bits) |  |  |  |

| LINDIV[8:0]                            | Bit time divider integer value                | 9           |  |  |  |

| LINMUL[4:0]                            | Bit time multiplier (master only)             | 5           |  |  |  |

| LINDFRAC[2:0]                          | Bit time divider fraction value (master only) | 3           |  |  |  |

The LIN bit rate *f*bit can be calculated from system clock *f*clk and bit timing registers according to the following equation.

$$Fbit = \frac{Fclk}{2* (LINDIV + LINDFRAC/8)* (LINMUL+1)}$$

The procedure of adjusting the bit timing registers is different between master and slave.

#### 8.2.1.1.4 Bit Timing Register Adjustment of Master

The steps for adjusting the bit timing registers of the master are explained in the following.

1. Setting up the bit time multiplier depending on used LIN data rate *f*bit according to the following equation:

$$LINMUL = \frac{20 \text{KBits/sec}}{Fbit} - 1$$

The value has to be rounded down to the next integer value.

1) Adjusting the bit time divider integer value depending on system clock, data rate and bit time multiplier according to the following equation:

$$LINDIV = \frac{Fclk}{2*(LINMUL+1)*(Fbit)}$$

The value has to be rounded down to the next integer value.

1.0 Adjusting the bit time divider fraction value depending on system clock, data rate, bit time multiplier and bit time divider integer according to the following equation:

$$LINDFRAC = \left(\frac{Fclk}{2*(LINMUL+1)*Fbit} - LINDIV\right)*8$$

The value has to be rounded down to the next integer value.

The table below shows sample values of the bit timing registers for different LIN data rates.

| Table 10 - LIN Timing Related Registers |               |          |    |   |  |  |  |

|-----------------------------------------|---------------|----------|----|---|--|--|--|

| System<br>Clock                         | LIN data rate | LINDFRAC |    |   |  |  |  |

|                                         | 19.2 Kbit/s   | 0        | 93 | 1 |  |  |  |

| 3.58 MHz                                | 9.6 Kbit/s    | 1        | 93 | 1 |  |  |  |

|                                         | 1 Kbit/s      | 19       | 89 | 4 |  |  |  |

#### 8.2.1.1.5 Bit Timing Register Adjustment of Slave

The steps for adjusting the bit timing registers of the LIN slave are explained in the following paragraphs.

Note: Register fields **LINMUL** and **LINDFRAC** do not exist in the slave. The LIN core slave synchronizes to any bit rate between 1 Kbit/s and 20 Kbit/s. Nevertheless, the bit timing registers have to be adjusted to adapt the LIN core to the used system clock frequency. Adjusting the bit time divider integer value depending on system clock according to the following equation:

$$LINDIV = \frac{Fclk}{40K}$$

For a system clock of 3.58MHz LINDIV = 89.5 = 89. (Always rounded down)

#### 8.2.1.2 Control of the LIN Module

The first step before transmitting messages with the LIN core is setting up the bit rate of the LIN system. For that, the host controller has to load the bit time registers, which has been explained in the previous sections. After that, the message transfer can be started. Controlling LIN core master and LIN core slave by the application is explained in the following.

#### 8.2.1.2.1 Controlling the LIN Master

The master is responsible for the schedule of the messages. It sends the header of each frame that contains SYNC BREAK FIELD, SYNC FIELD and IDENTIFIER FIELD. The steps for scheduling a message frame are explained in the following.

- 1. The following steps have to be done by the application when an interrupt is requested.

- Check the LIN\_ERR bit (LINSTATUS). Perform error handling and proceed to step d if bit ERROR is set, otherwise proceed to step b.

- Check the LIN\_WAKEUP bit (LINSTATUS) it is set if the master has received or transmitted a wakeup signal. Proceed with the step d if LIN\_WAKEUP is set else proceed with step c.

- Check the LIN\_CMPLT (LINSTATUS) it is set if the transfer was successful. If LIN\_CMPLT is set and the current frame was a receive operation load the received data from the data buffer.

- Set the LIN\_RST\_INT and LIN\_RST\_ERROR bits (LINCONTROL) register to reset the interrupt request and the error flags.

#### 8.2.1.2.2 Controlling the LIN Slave

The LIN core slave detects the header of the message frame sent by the LIN master and synchronizes its internal bit time to the master bit time. An interrupt is requested after the reception of the IDENTIFIER FIELD, after the reception of a wakeup signal (if the slave is in sleep mode), when an error is detected or when the message transfer is completed.

The following steps have to be done by the application when an interrupt is requested.

- Check the LIN\_DATA\_REQ bit (LINSTATUS) (it is 1 when the IDENTIFIER FIELD has been received). Proceed with the following if LIN\_DATA\_REQ is set else proceed with step 2.

- Load the identifier from the LINID register and process it.

- Adjust the **LINTX** bit (1 if the current frame is a transmit operation for the slave, 0 if the current frame is a receive operation for the slave).

- Load the data length in the **LINLENGTH** register (number of data bytes or value "1111b" if the data length should be decoded from the identifier) and set the checksum type (enhanced or classic).

- Load the data to transmit into the data buffer (for transmit operation only).

- Set the LINACK bit (LINCONTROL) register.

Note 1: Steps <u>a</u> thru <u>e</u> have to be done during the IN-FRAME RESPONSE SPACE, if the current frame is a transmit operation for the slave; otherwise a timeout will be detected by the master. If the current frame is a receive operation for the slave, steps <u>a</u> thru <u>e</u> have to be finished until the reception of the first byte after the IDENTIFIER FIELD. Otherwise, the internal receive buffer of the slave core will be overwritten and a timeout error will be detected in the slave core.

Note 2: If the application of the slave detects an unknown identifier (e.g. extended identifier = 0x3E) it has to write a 1 to bit **LIN\_SLAVE\_STOP** (**LINCONTROL**) instead of setting the **LINACK** bit (steps <u>b</u> thru <u>e</u> can be skipped). In that case the LIN core slave stops the processing of the LIN communication until the next SYNC BREAK is received.

1. Check the LIN\_ERR (LINSTATUS). Perform error handling and proceed with step 6 if bit LIN\_ERR is set else proceed with step 3.

Note 3: Bit **LIN\_TOUT\_ERR** and bit **LIN\_WAKEUP** are set if the slave has sent a wakeup signal but the master did not respond within 150 ms.

- 2. Check bit LIN\_IDL\_TOUT (LINSTATUS) is set and activate the sleep mode by setting bit LINSLEEP if it is.

- 3. Check bit LIN\_WAKEUP it is set if the slave has received a wakeup signal. If LIN\_WAKEUP is set proceed with step 6 else proceed with step 5.

Note 4: Bit **LIN\_CMPLT** is not changed when a wake-up signal is transmitted or received. Therefore, bit **LIN\_WAKEUP** has to be checked before bit **LIN\_CMPLT**.

- 3. Check LIN\_CMPLT bit in the LINSTATUS register (it is set if the transmission was successful). If LIN\_CMPLT is set and the current frame was a receive operation for the slave, load the received data bytes from the data buffer.

- 4. Set the bits **LIN\_RST\_INT** and **LIN\_RST\_ERR** in the control register to reset the interrupt request and the error flags.

#### 8.2.1.2.3 Sleep Mode and Wakeup

To reduce the systems power consumption the LIN Protocol Specification defines a Sleep Mode. The message used to broadcast a Sleep Mode request has to be started by the host controller of the LIN core master in the same way as a normal transmit message. The host controller of the LIN core slave has to decode the Sleep Mode Frame from Identifier and data bytes. After that, it has to put the LIN slave node into the Sleep Mode by setting bit **LINSLEEP** in the control register. If bit **LINSLEEP** in the control register of the LIN core slave is not set and there is no bus activity for 4 s to 10 s (specified bus idle timeout) bit **LIN\_IDL\_TOUT** is set and an interrupt request is generated. After that application may assume that the LIN bus is in Sleep Mode and set bit **LINSLEEP** in the **LINCONTROL** register of the LIN core slave. The bus inactivity time which should be defined as bus idle timeout for the slave can optionally set to values 4s, 6s, 8s or 10s as possible accordingly with specification 2.0.

Sending a Wakeup signal with the master or any slave node terminates the Sleep Mode of the LIN bus. To send a Wakeup signal, the host controller of the LIN core has to set the bit **LIN\_WAKEUP** in the **LINSTATUS** register. After successful transmission of the wakeup signal with the LIN core master the **LIN\_WAKEUP** bit in the **LINSTATUS** register of the sending LIN core master is set and an interrupt request is generated. The LIN core slave does not generate an interrupt request after successful transmission of the Wakeup signal but it generates an interrupt request if the master does not respond to the Wakeup signal within 150 msec. to 250 msec. This value can be set optionally to 180ms, 200ms, 220ms or 240ms as it is possible accordingly with specification 2.0. In that case, bit **LIN\_ERR** and bit **LIN\_TOUT\_ERR** are set. The host controller has to decide whether to transmit another Wakeup signal or not.

All LIN cores that detect a wakeup signal will set the bit LIN\_WAKEUP and generate an interrupt request to their host controller. The inverted bit LINSLEEP is connected to the output LIN\_TR\_EN. Bit LINSLEEP is automatically reset and LIN\_TR\_EN (whose polarity can be flipped by setting/clearing LINTRAN) is set to high when the LIN core detects a wakeup signal. Output LIN\_TR\_EN may be used for connecting the enable signal of the LIN transceiver. It depends on the transceiver type whether this is possible or not.

#### 8.2.1.2.4 Error Detection and Handling

The LIN core generates an interrupt request and stops the processing of the current frame if it detects an error. The application has to check the type of error by processing the LINERROR register. After that, it has to reset the LINERROR register and the LIN\_ERR bit in status register by writing a 1 to bit LIN\_RST\_ERR in control register. Starting a new message with the LIN core master or sending a Wakeup signal with master or slave is possible only if bit LIN\_ERR in LINSTATUS register is 0.

#### 8.2.1.3 LIN Registers

The following registers are available:

| LIN_DA                          | TAn  | 0x5000 | 0030/1/2/3 | 3/4/5/6/7 | 0x00 |      |      |  |

|---------------------------------|------|--------|------------|-----------|------|------|------|--|

| R/W                             | R/W  | R/W    | R/W        | R/W       | R/W  | R/W  | R/W  |  |

| LDT7                            | LDT6 | LDT5   | LDT4       | LDT3      | LDT2 | LDT1 | LDT0 |  |

| MSB                             |      |        |            |           |      |      | LSB  |  |

| Bit7-0 LDT7-LDT0: LIN data bits |      |        |            |           |      |      |      |  |

LIN\_DATAn: LIN data registers. (n = 0, 1, ..., 7)

LINCTRL: LIN control register.

| LINCTRL | INCTRL 0x50000038 |       | 0x00   |             |             |                  |                   |

|---------|-------------------|-------|--------|-------------|-------------|------------------|-------------------|

| W       | R/W               | R/W   | R/W    | W           | W           | R/W              | R/W               |

| LINSTOP | LINSLEEP          | LINTX | LINACK | LIN_RST_INT | LIN_RST_ERR | LIN_WKUP_<br>REQ | LIN_START_R<br>EQ |

| MSB     |                   |       |        |             |             |                  | LSB               |

## INDIE

|      | LINSTOP: LIN Stop command (slave only): The host has to write a '1' to this bit if it handles a data<br>t interrupt and cannot make use of the frame content with the received identifier (e.g. extended identifiers). For<br>the LIN slave stops the processing of the LIN communication until the next SYNC BREAK is detected.         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 0 = No action                                                                                                                                                                                                                                                                                                                            |

|      | 1 = STOP                                                                                                                                                                                                                                                                                                                                 |

| Bit6 | <b>LINSLEEP:</b> LIN Sleep command: The bit is used by the LIN core to determine whether the LIN bus is in Sleep Mode or not. The application has to set the bit after sending or receiving a Sleep Mode frame or if a bus idle timeout interrupt is requested. The bit will be reset by the LIN core, when a wakeup signal is detected. |

|      | 0 = LIN interface is not in sleep mode                                                                                                                                                                                                                                                                                                   |

|      | 1 = LIN interface is in sleep mode                                                                                                                                                                                                                                                                                                       |

| Bit5 | <b>LINTX:</b> LIN transmit command: The bit determines whether the current frame is a transmit frame or a receive frame for the LIN node. It has to be set by the application.                                                                                                                                                           |

|      | 0 = LIN interface is receiving                                                                                                                                                                                                                                                                                                           |

|      | 1 = LIN interface is transmitting                                                                                                                                                                                                                                                                                                        |

| Bit4 | <b>LINACK:</b> LIN data acknowledge (slave only): The bit has to be set by the application after handling a data request interrupt (compare bit LIN_DT_REQ in LINSTATUS register). The bit will be reset by the LIN core.                                                                                                                |

|      | 0 = Acknowledge not requested or already reset by core                                                                                                                                                                                                                                                                                   |

|      | 1 = LIN interface acknowledge request                                                                                                                                                                                                                                                                                                    |

| Bit3 | LIN_RST_INT: LIN reset interrupt: The application has to write a '1' to this bit to reset the LIN_INT_REQ bit in the LINSTATUS register.                                                                                                                                                                                                 |

|      | 0 = No Interrupt reset request                                                                                                                                                                                                                                                                                                           |

|      | 1 = Reset of interrupt request                                                                                                                                                                                                                                                                                                           |

| Bit2 | LIN_RST_ERR: LIN reset error: The application has to write a '1' to this bit                                                                                                                                                                                                                                                             |

|      | to reset the error bits in status register and error register.                                                                                                                                                                                                                                                                           |

|      | 0 = No errors reset request                                                                                                                                                                                                                                                                                                              |

|      | 1 = Errors reset request                                                                                                                                                                                                                                                                                                                 |

| Bit1 | LIN_WKUP_REQ: LIN Wake-Up request: The bit has to be set by the application to                                                                                                                                                                                                                                                           |

|      | terminate the Sleep Mode of the LIN bus by sending a Wakeup signal. The bit will be reset by the LIN core.                                                                                                                                                                                                                               |

|      | 0 = No wake-up request                                                                                                                                                                                                                                                                                                                   |

|      | 1 = Wake-up request                                                                                                                                                                                                                                                                                                                      |