# iND83231 "Krankl"

indie's highly integrated 400MHz transceiver with integrated MCU and high power supply

12/23/2015

Preliminary Data sheet

# **1** Document Revision History

Table 1 Revision History

| Rev # | Date                       | Description                                                                                                                                                                                                                                                                          | Ву  |

|-------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 0.1   | June 17 <sup>th</sup> 2014 | Initial version (collected from AyDeeKay documentation)                                                                                                                                                                                                                              | GKo |

| 0.2   | Aug. 24 <sup>th</sup> 2014 | 1 <sup>st</sup> release                                                                                                                                                                                                                                                              | GKo |

| 1.1   | Apr. 15 <sup>th</sup> 2015 | <ul> <li>Updated:</li> <li>Ported doc to product spec type with indie format</li> <li>Adjusted reference to 12MHz RC</li> <li>Pin list – naming updated – created pin mux table</li> <li>Added summary reg tables for GIO, SIO, etc</li> <li>Electrical table centralized</li> </ul> | LF  |

| 1.2   | 12/23/15                   | Format change, modified table                                                                                                                                                                                                                                                        | CR  |

| 1.21  | 5/16/15                    | Product number change for consistency                                                                                                                                                                                                                                                | PH  |

# 2 Table of Content

| 1 | Doc                                                                                            | ument Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2                                                                                |

|---|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2 | Tabi                                                                                           | le of Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3                                                                                |

| 3 | Gen                                                                                            | eral Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                                                |

|   | 3.1                                                                                            | CPU Architecture:                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                |

|   | 3.2                                                                                            | Memory:                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                |

|   |                                                                                                | ISM band 433.92MHz ASK/OOK Radio:                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

|   |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|   |                                                                                                | Peripherals:                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|   | 3.5                                                                                            | Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                                                                                |

|   | 3.6                                                                                            | Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                                |

|   | 3.7                                                                                            | Device overview                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8                                                                                |

|   | 3.8                                                                                            | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                                                |

|   | 3.8                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|   |                                                                                                | 8.2 Pin List                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|   | 3.8                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|   | 3.8                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| 4 | Abs                                                                                            | olute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14                                                                               |

| 5 | Fund                                                                                           | ctional blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15                                                                               |

|   | 5.1                                                                                            | ARM Cortex M0 Microcontroller Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

|   | 5.1                                                                                            | Ann contex mo microcontroller Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                               |

|   |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|   | 5.1                                                                                            | 1.1 Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15                                                                               |

|   | 5.1<br>5.1                                                                                     | 1.1 Memory Map<br>1.2 Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15<br>18                                                                         |

|   | -                                                                                              | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)                                                                                                                                                                                                                                                                                                                                                                                        | 15<br>18<br>21                                                                   |

|   | 5.1<br>5.1                                                                                     | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)                                                                                                                                                                                                                                                                                                                                                                                        | 15<br>18<br>21<br>23                                                             |

|   | 5.1<br>5.1<br><i>5.2</i>                                                                       | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)         1.4       Interrupt Vectors                                                                                                                                                                                                                                                                                                                                                    | 15<br>21<br>23<br>25                                                             |

|   | 5.1<br>5.1<br>5.2<br>5.2                                                                       | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)         1.4       Interrupt Vectors <i>RF Receiver Subsystem</i>                                                                                                                                                                                                                                                                                                                       | 15<br>21<br>23<br>25<br>27                                                       |

|   | 5.1<br>5.1<br>5.2<br>5.2<br>5.3                                                                | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)         1.4       Interrupt Vectors <i>RF Receiver Subsystem</i> 2.1       RF Receiver Registers                                                                                                                                                                                                                                                                                       | 15<br>21<br>23<br>25<br>27<br>42                                                 |

|   | 5.1<br>5.2<br>5.2<br>5.3<br>5.3                                                                | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)         1.4       Interrupt Vectors <i>RF Receiver Subsystem</i> 2.1       RF Receiver Registers <i>RF Transmitter Subsystem</i>                                                                                                                                                                                                                                                       | 15<br>18<br>21<br>23<br>25<br>27<br>42<br>44                                     |

|   | 5.1<br>5.2<br>5.2<br>5.3<br>5.3                                                                | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)         1.4       Interrupt Vectors         1.4       Interrupt Vectors         2.1       RF Receiver Subsystem         2.1       RF Receiver Registers         8.1       Fractional PLL         3.2       Transmission State Machine Operation                                                                                                                                        | 15<br>18<br>21<br>23<br>25<br>27<br>42<br>44<br>44                               |

|   | 5.1<br>5.2<br>5.2<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3                                           | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)         1.4       Interrupt Vectors         1.4       Interrupt Vectors         2.1       RF Receiver Subsystem         2.1       RF Receiver Registers         RF Transmitter Subsystem         3.1       Fractional PLL         3.2       Transmission State Machine Operation                                                                                                       | 15<br>18<br>21<br>23<br>25<br>27<br>42<br>44<br>44<br>45                         |

|   | 5.1<br>5.2<br>5.2<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3                                           | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)         1.4       Interrupt Vectors <i>RF Receiver Subsystem</i> 2.1       RF Receiver Registers <i>RF Transmitter Subsystem</i> 3.1       Fractional PLL         3.2       Transmission State Machine Operation         3.3       Chip Rate Selection                                                                                                                                 | 15<br>21<br>23<br>25<br>27<br>42<br>44<br>44<br>45<br>50                         |

|   | 5.1<br>5.2<br>5.2<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3                                    | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)         1.4       Interrupt Vectors <i>RF Receiver Subsystem</i> 2.1         2.1       RF Receiver Registers <i>RF Transmitter Subsystem</i> 3.1         Fractional PLL       3.2         3.3       Chip Rate Selection         3.4       Transmitter registers <i>RF Switch RF Switch</i>                                                                                             | 15<br>21<br>23<br>25<br>27<br>42<br>44<br>44<br>45<br>50<br>64                   |

|   | 5.1<br>5.2<br>5.2<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3                                    | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)         1.4       Interrupt Vectors <i>RF Receiver Subsystem</i> 2.1       RF Receiver Registers <i>RF Transmitter Subsystem</i> 3.1       Fractional PLL         3.2       Transmission State Machine Operation         3.3       Chip Rate Selection         3.4       Transmitter registers <i>RF Switch RF Switch</i>                                                              | 15<br>21<br>23<br>25<br>27<br>42<br>44<br>44<br>45<br>50<br>64<br>65             |

|   | 5.1<br>5.2<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.4<br>5.5<br>5.5 | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)         1.4       Interrupt Vectors         1.4       Interrupt Vectors         2.1       RF Receiver Subsystem         2.1       RF Receiver Registers         2.1       RF Receiver Registers         3.1       Fractional PLL         3.2       Transmission State Machine Operation         3.3       Chip Rate Selection         3.4       Transmitter registers <i>RF Switch</i> | 15<br>21<br>23<br>25<br>27<br>42<br>44<br>44<br>45<br>50<br>64<br>65<br>65       |

|   | 5.1<br>5.2<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.3<br>5.4<br>5.5<br>5.5 | 1.1       Memory Map         1.2       Timers         1.3       Watch Dog Timer (WDT)         1.4       Interrupt Vectors <i>RF Receiver Subsystem</i>                                                                                                                                                                                                                                                                                                                       | 15<br>21<br>23<br>25<br>27<br>42<br>44<br>44<br>45<br>60<br>64<br>65<br>65<br>66 |

|            | 5.5.5     | ADC Registers                                    | 69  |

|------------|-----------|--------------------------------------------------|-----|

| 5.6        | 6 Pulse   | Width Modulators (PWM)                           |     |

|            |           | PWM Usage Description                            |     |

|            | 5.6.2     | PWM Registers                                    |     |

| <b>-</b> - | 7         | Creasing Course (ZCC)                            |     |

|            |           | Crossing Sense (ZCS)                             |     |

|            | 5.7.1     | ZCS Usage Description                            | 80  |

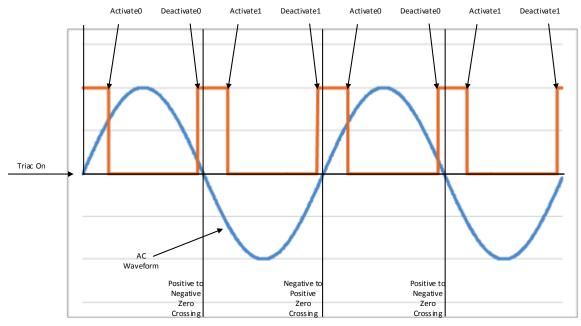

| 5.8        | 5         | al Triac Timer                                   |     |

|            |           | Digital Triac Timer Usage Description            |     |

|            | 5.8.2     | DTT Control Register Map                         | 89  |

| 5.9        | ) Seria   | l Interfaces                                     |     |

|            |           | UART                                             |     |

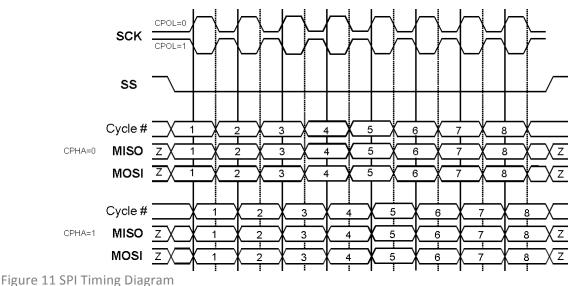

|            | 5.9.2     | SPI Interface                                    |     |

| <b>5</b> 1 |           | S                                                | 111 |

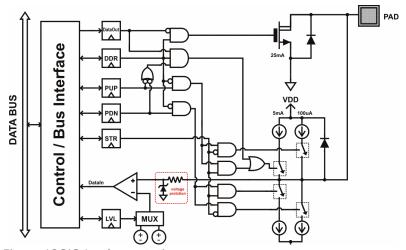

|            | 5.10.1    | General Purpose IO (GIO)                         |     |

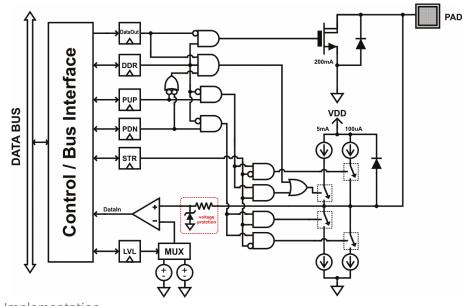

|            | 5.10.1    | High Current Pull down IO (SIO)                  |     |

|            | 5.10.2    | GIO and SIO Connections to ADC                   |     |

|            | 5.10.4    | Port Configuration Registers                     |     |

|            | 5.10.5    | GIO PA Configuration Registers                   |     |

|            | 5.10.6    | SIO PC Configuration Registers                   |     |

|            | 5.10.7    | GPIO PD Configuration Registers                  |     |

|            | 5.10.8    | GPIO PE Registers                                |     |

|            | 5.10.9    | GPIO PF Registers                                |     |

| 51         | 1 Clock   | sources                                          | 155 |

|            | 5.11.1    | Clock Source Operation and Description           |     |

|            | 5.11.2    | Clock Related Registers                          |     |

|            | -         | -                                                |     |

|            |           | er Management Unit                               |     |

|            | 5.12.1    | PMU control of Reset                             |     |

|            | 5.12.2    | PMU control of sleep and deep sleep (halt) modes |     |

|            | 5.12.3    | PMU control of Brownout                          |     |

|            | 5.12.4    | PMU Registers                                    |     |

| 5.1        | 3 Wake    | e Up Timer                                       |     |

|            | 5.13.1    | Wake-Up Timer Operation and Description          |     |

|            | 5.13.2    | Wake-Up Timer Register                           |     |

| 6 E        | lectrical | Characteristics                                  |     |

|            |           |                                                  |     |

| 7 B        | ill of Ma | terial                                           | 170 |

| 8 P        | ackage (  | Dutline                                          |     |

| 9 R        | eference  | es                                               |     |

|            |           |                                                  |     |

| 10         | Contact   | S                                                |     |

# **3** General Description

# Main Features:

- 433.92 MHz ASK Transceiver with physical layer decoder

- ARM Cortex M0 32-bit µC Low Power

- 160kB embedded Flash Memory and 8kB SRAM

- Supports UART and SPI peripheral interfaces

- Single 30MHz Crystal clock oscillator

- Fully integrated Power management subsystem.

- Runs directly from high operating voltage 9V to 32V, with a maximum of 45V

- Nineteen 3.3V Low Voltage GPIOs

- Seven 12V GPIOs, sink up to 25mA to GND

- Two 12V high current sink GPIOs, sink up to 200mA to GND (Relay Driver)

- Protected high current pull downs

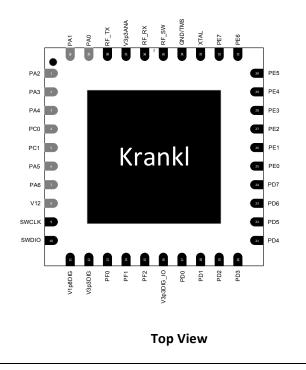

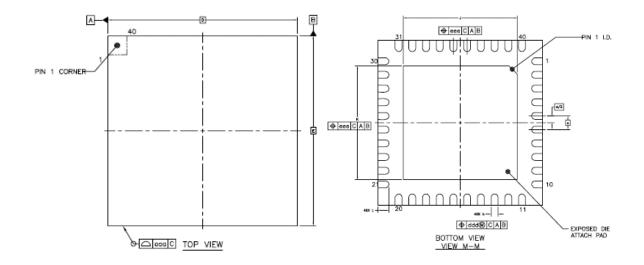

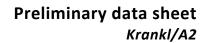

Package:

QFN 6mm x 6mm 40-Pins

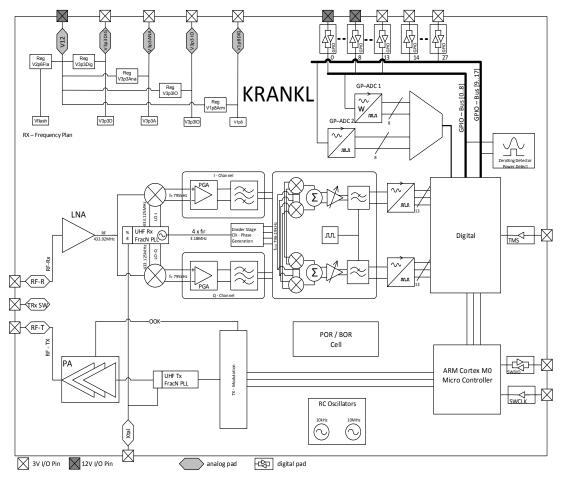

This ASIC has an integrated super-heterodyne ISM band, 433.92MHz, ASK transceiver. The oscillator frequency for the RF is generated by fractional-N type frequency synthesizers from a crystal oscillator. This ASIC integrates the following features:

## **3.1 CPU Architecture:**

- ARM Cortex-M0 processor

- System Tick Timer (SysTick 24 bits, interruptible)

- 3 additional 32-bit timers

- Serial Wire Debugger

- Built-in Nested Vectored Interrupt Controller (NVIC)

- Programmable Watch-Dog Timer

## 3.2 Memory:

- 160kByte of Flash Program Memory

- 8kByte of SRAM

# 3.3 ISM band 433.92MHz ASK/OOK Radio:

- A super-heterodyne receiver, with up to -110dBm of sensitivity

- A Transmitter supporting with a maximum output power of +13dBm

- Integrated fractional-N phase locked loop (PLL) referenced to crystal oscillator

# 3.4 Peripherals:

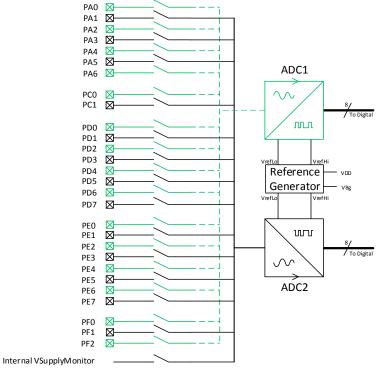

- Two 8 bits SAR ADC, with a total of 29 input channels connected to the GPIOs and 12V supply along with selectable input voltage references for increased resolution.

- 3 PWM channels

- 28 general purpose IO ports

- 7 high voltage (9-35V) general purpose IO ports which can source 5mA or sink 25mA (PA[0-6])

- 2 high voltage (9-35V) general purpose IO ports, which can sink 200mA in order to directly drive a relay coil (PC[0/1])

- 19 low voltage (3.3V nominal) general purpose IO ports (PD[0-7], PE[0-7], PF[0-2])

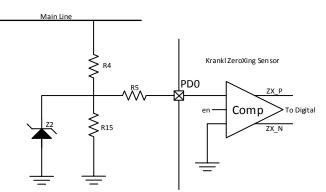

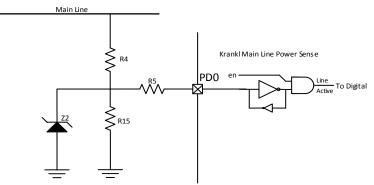

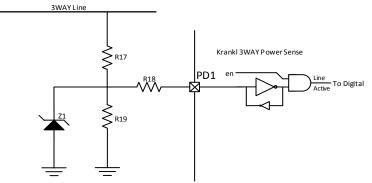

- 2 Dedicated IOs for Zero Crossing and Power Sense Detection used for Light Timing and 3 Way Switch input.

- Integrated Power Management

- Dedicated Wake-up Timer

- Zero crossing Detector and Power Sense Functionality

# 3.5 Clocks

Krankl integrates three oscillators which may be used to generate a time base

- a 30MHz high accuracy crystal oscillator, which is used as a reference for the RF

- a 12MHz, 5% accurate RC oscillator, for current saving operation

- a 10kHz, low power oscillator permanently activated for house keeping

# 3.6 Reliability

Krankl is designed to withstand load dump events of up to 45V on its supply pin and on every high voltage IO. It is also designed to withstand electrical discharges to its 12V IOs according to ISO10605.

## 3.7 Device overview

Figure 1 depicts a high-level block diagram of the Krankl device. The application subsystems can be grouped into several types: RF receiver, RF transmitter, power management, general purpose IO ports, clock generation, zero crossing detect, power on reset, brown out reset, and micro controller unit.

Figure 1 Functional Block

The microcontroller debug and access port consists of clock (SWCLK) and data (SWDIO) signals. The interface operates at a typical 3.3V CMOS level and is intended to handle communication between an external debugger and Krankl IC.

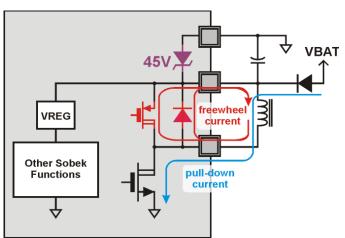

The general-purpose ports handle basic IO functions with any 12-24V system, such as sensing switch states and driving relays. Each driver is capable of 25mA pull-down and 5mA pull-up to Supply/ground levels when configured as outputs. A subset of the pins (SIO type) are capable of 200mA pull down with 5mA pull-up capability. The high current ports are intended to be used to drive relays, and will be protected against over-current, over-temperature.

The high-current ports (PC0/1) have an auto shutdown capability to place the port into tristate mode

if a short-circuit condition is detected in the current path they control. The short-circuit is detected using a circuit which monitors the voltage drop across a PCB trace in-line with the current path, which should be connected to the appropriate differential sense pins on Krankl. Any time the current sensed is above a threshold (differential 1V across the PCB trace), the port will automatically enter a latched tristate mode, which can be recycled by software.

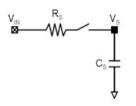

The clock generation subsystem consists of a single ended crystal oscillator. The crystal oscillator will be configured to operate with the crystal connected between a single pin and ground. This pin can be used alternately as an external clock source just by driving it with a digital level. When operating with a crystal, a 100nF series dc block capacitor is required between crystal and this pin in order to avoid premature aging of crystal and/or unstable oscillation.

The power management portion consists of a bandgap voltage reference and several linear voltage regulators. The voltage reference is used to provide the reference voltage for the voltage regulators, as well as for other circuits internal, such as, for example, the A/D converters. A voltage regulator provides power for the internal 3.3V digital logic (V3P3DIG) and the bus interface, and is available at a pin to allow placement of a bypass capacitor and to allow it to be used as the power source for the microcontroller. Another 3.3V regulator supplies power to the majority of on-chip analog functions (V3P3ANA). The ARM Cortex M0 micro controller unit requires a 2.6V power supply for the embedded flash memory and a 1.8V supply for the micro controller core unit, each is sourced from a separate voltage regulator. Krankl utilizes a dedicated regulator for its 3.3V GPIO circuitry.

The RF receiver is configured to receive and decode ASK (OOK) modulated messages with nominal carrier frequency of 433.92MHz ±100KHz. Messages are fully decoded and buffered without microcontroller intervention. The transmitter is capable to transmit ASK coded signal at 433.92MHz.

# 3.8 Pin Description

## 3.8.1 Pin Types

- SUPPLY=Supply Pin or Decoupling Pin for internal Supply Regulator

- ANAIN=Analog Input, ANAOUT=Analog Output, ANAIO=Analog Input/Output.

- DIGIO=Digital IO

- VREG= Regulated Output, SUPPLY=Supply input Pin

- GIO = General Purpose IO, 25mA pull-down and 5mA pull-up

- SIO = General Purpose IO with 200mA pull-Down and 5mA pull-up

- GND= Ground

- Not Connected (NC)

## 3.8.2 Pin List

Table 2 Pin List

| #  | Pin Name   | Туре   | Voltage | Description                                            |

|----|------------|--------|---------|--------------------------------------------------------|

| 1  | PA2        | GIO    | 12V     | High Voltage General Purpose IO                        |

| 2  | PA3        | GIO    | 12V     | High Voltage General Purpose IO                        |

| 3  | PA4        | GIO    | 12V     | High Voltage General Purpose IO                        |

| 4  | PC0        | SIO    | 12V     | High Voltage General Purpose IO with high current sink |

| 5  | PC1        | SIO    | 12V     | High Voltage General Purpose IO with high current sink |

| 6  | PA5        | GIO    | 12V     | High Voltage General Purpose IO                        |

| 7  | PA6        | GIO    | 12V     | High Voltage General Purpose IO                        |

| 8  | V12        | SUPPLY | 12V     | 12V Power supply                                       |

| 9  | SWCLK      | DIGIO  | 3.3V    | SWD Debug/MCU clock access port                        |

| 10 | SWDIO      | DIGIO  | 3.3V    | SWD Debug/MCU data access port                         |

| 11 | V1P8DIG    | SUPPLY | 3.3V    | Voltage regulator output: 1.8V                         |

| 12 | V3P3DIG    | SUPPLY | 3.3V    | Voltage regulator output: 3.3V digital Core Supply     |

| 13 | PF0        | GPIO   | 3.3V    | General Purpose IO                                     |

| 14 | PF1        | GPIO   | 3.3V    | General Purpose IO                                     |

| 15 | PF2        | GPIO   | 3.3V    | General Purpose IO                                     |

| 16 | V3P3DIG_IO | SUPPLY | 3.3V    | Voltage regulator output: 3.3V IO supply               |

| 17 | PD0        | GPIO   | 3.3V    | General Purpose IO                                     |

| 18 | PD1        | GPIO   | 3.3V    | General Purpose IO                                     |

| 19 | PD2        | GPIO   | 3.3V    | General Purpose IO                                     |

| 20 | PD3        | GPIO   | 3.3V    | General Purpose IO                                     |

| 21 | PD4        | GPIO   | 3.3V    | General Purpose IO                                     |

| 22 | PD5        | GPIO   | 3.3V    | General Purpose IO                                     |

| 23 | PD6        | GPIO   | 3.3V    | General Purpose IO                                     |

| 24 | PD7        | GPIO   | 3.3V    | General Purpose IO                                     |

| 25 | PEO        | GPIO   | 3.3V    | General Purpose IO                                     |

| #  | Pin Name | Туре   | Voltage | Description                                  |

|----|----------|--------|---------|----------------------------------------------|

| 26 | PE1      | GPIO   | 3.3V    | General Purpose IO                           |

| 27 | PE2      | GPIO   | 3.3V    | General Purpose IO                           |

| 28 | PE3      | GPIO   | 3.3V    | General Purpose IO                           |

| 29 | PE4      | GPIO   | 3.3V    | General Purpose IO                           |

| 30 | PE5      | GPIO   | 3.3V    | General Purpose IO                           |

| 31 | PE6      | GPIO   | 3.3V    | General Purpose IO                           |

| 32 | PE7      | GPIO   | 3.3V    | General Purpose IO                           |

| 33 | XTAL     | ANAIO  | 3.3V    | IO Crystal Oscillator, Single clock input    |

| 34 | GND/TMS  | DIGIO  | 3.3V    | Input test mode state, GND in mission mode   |

| 35 | RF-SW    | ANAIO  | 3.3V    | TRX filter switch                            |

| 36 | RF-RX    | ANAIN  | 3.3V    | IO RX path 433MHz                            |

| 37 | V3P3ANA  | SUPPLY | 3.3V    | Voltage regulator output, 3.3V analog supply |

| 38 | RF-TX    | ANAOUT | 3.3V    | IO TX path 433MHz                            |

| 39 | PA0      | GIO    | 12V     | High Voltage General Purpose IO              |

| 40 | PA1      | GIO    | 12V     | High Voltage General Purpose IO              |

#### 3.8.3 **Pin State upon Power-On Reset**

- Unless otherwise noted, all pins default to tristate (high impedance) upon power-on reset.

- Pins otherwise noted include:

- SUPPLY pins.

- VREG pins: output a regulator voltage upon power-on reset are at specified voltage levels in the presence of 12V supply.

- RF pins are configurable via SW to enter tristate

## 3.8.4 Alternative pin functions

| Ta | ab | le | 3 | Pin | Μ | uxing |  |

|----|----|----|---|-----|---|-------|--|

|----|----|----|---|-----|---|-------|--|

| #  | Pin Name | FO       | F1 (PWX) | F2 (ADC) |

|----|----------|----------|----------|----------|

| 1  | PA2      |          |          | ADC1     |

| 2  | PA3      |          |          | ADC2     |

| 3  | PA4      |          |          | ADC1     |

| 4  | PC0      |          | PWM2     | ADC1     |

| 5  | PC1      |          |          | ADC2     |

| 6  | PA5      |          | PWM1     | ADC2     |

| 7  | PA6      |          |          | ADC1     |

| 8  | V12      | -        | -        | -        |

| 9  | SWCLK    | -        | -        | -        |

| 10 | SWDIO    | -        | -        | -        |

| 11 | V1P8DIG  | -        | -        | -        |

| 12 | V3P3DIG  | -        | -        | -        |

| 13 | PF0      |          |          | ADC1     |

| 14 | PF1      |          |          | ADC2     |

| 15 | PF2      |          |          | ADC1     |

| 16 | V3P3DIG  | -        | -        | -        |

| 17 | PD0      |          |          | ADC1     |

| 18 | PD1      |          |          | ADC2     |

| 19 | PD2      |          | PWM2     | ADC1     |

| 20 | PD3      |          | PWM1     | ADC2     |

| 21 | PD4      |          | PWM3     | ADC1     |

| 22 | PD5      |          | PWM3     | ADC2     |

| 23 | PD6      |          |          | ADC1     |

| 24 | PD7      |          |          | ADC2     |

| 25 | PE0      | SPI_CS_n |          | ADC1     |

| 26 | PE1      | SPI_MISO |          | ADC2     |

| 27 | PE2      | SPI_SCK  |          | ADC1     |

| #  | Pin Name | FO       | F1 (PWX) | F2 (ADC) |

|----|----------|----------|----------|----------|

| 28 | PE3      | SPI_MOSI |          | ADC2     |

| 29 | PE4      | UART_RX  |          | ADC1     |

| 30 | PE5      | UART_TX  |          | ADC2     |

| 31 | PE6      |          |          | ADC1     |

| 32 | PE7      |          |          | ADC2     |

| 33 | XTAL     | -        | -        | -        |

| 34 | GND/TMS  | -        | -        | -        |

| 35 | RF-SW    | -        | -        | -        |

| 36 | RF-RX    | -        | -        | -        |

| 37 | V3P3ANA  | -        | -        | -        |

| 38 | RF-TX    | -        | -        | -        |

| 39 | PA0      |          |          | ADC1     |

| 40 | PA1      |          |          | ADC2     |

# 4 Absolute Maximum Ratings

| Absolute Maximum Ratings, Voltages Referenced to Ground  |                                                                      |      |             |      |  |

|----------------------------------------------------------|----------------------------------------------------------------------|------|-------------|------|--|

| Name                                                     | Conditions                                                           | Min  | Max         | Unit |  |

| 12V Supply voltage (12V nominal)                         | Short duration, no long term damage                                  | -0.3 | +45         | V    |  |

| GIO voltage                                              | configured as input, no<br>damage -0.3 V12+0.3                       |      | V           |      |  |

| SIO voltage                                              | configured as input, no<br>damage                                    | -0.3 | V12+0.3     | V    |  |

| 3.3V GPIO configured as input, no damage                 |                                                                      | -0.3 | V3p3DIG+0.3 | V    |  |

| 3V Analog IO                                             | XTAL and RF, no damage                                               | -0.3 | V3p3AN+0.3  | V    |  |

| Operating Temp. de-rated performance, full functionality |                                                                      | -40  | +85         | °C   |  |

| ESD/Transient Robustness                                 |                                                                      |      |             |      |  |

| Storage Temperature                                      | de-rated performance, full functionality                             | -55  | +150        | °C   |  |

| HBM (all pins)                                           | any pin to any other pin or ground, loose part                       | -4   | 4           | kV   |  |

| HBM (GIO, SIO)                                           | to other pin in group or<br>ground, soldered to<br>application board | -6   | 6           | kV   |  |

| CDM                                                      | no damage                                                            | -300 | 300         | V    |  |

| MM                                                       | no damage                                                            | -150 | 150         | V    |  |

Table 4 Absolute Maximum Ratings

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximumrated conditions for extended periods may affect device reliability.

# 5 Functional blocks

## 5.1 ARM Cortex M0 Microcontroller Subsystem

Krankl device includes an embedded microcontroller subsystem, which is based on the ARM Cortex M0 core. It includes a program flash memory of 160kBytes, and an SRAM of 8kBytes. It includes three 32-bit timers, plus a dedicated watchdog timer. Additionally, it includes a **N**ested **V**ector Interrupt **C**ontroller (NVIC) to scheduled hardware interrupts, and a **W**akeup Interrupt **C**ontroller (WIC), which enable the control of the various power modes.

#### 5.1.1 Memory Map

| System Memory Map       |            |                                |           |  |  |

|-------------------------|------------|--------------------------------|-----------|--|--|

| Address                 | Memory     | Description                    | Reference |  |  |

| 0x00000000 - 0x00027FFF | Flash      | 160kByte Flash Memory          | N/A       |  |  |

| 0x00028000 - 0x0003FFFF | N/A        | Reserved                       | N/A       |  |  |

| 0x00040000 - 0x000400FF | Flash      | 256Byte 1st NVR Sector         | N/A       |  |  |

| 0x00040100 - 0x000401FF | Flash      | 256Byte 2nd NVR Sector         | N/A       |  |  |

| 0x00040200 - 0x1FFFFFFF | N/A        | Reserved                       | N/A       |  |  |

| 0x20000000 - 0x20001FFF | SRAM       | 8kByte SRAM                    | N/A       |  |  |

| 0x20002000 - 0x4FFFFFFF | N/A        | Reserved                       | N/A       |  |  |

| 0x50000000 - 0x5000007F | Peripheral | 128Byte peripheral fast access |           |  |  |

| 0x50000080 - 0x50000085 | Peripheral | 6Byte Block Transfer control   | N/A       |  |  |

| 0x50000086 - 0x5000FFFF | N/A        | Reserved                       | N/A       |  |  |

| 0x50010000 - 0x5001FFFF | Peripheral | 64kByte peripheral slow access |           |  |  |

Table 5 System Memory Map

| System Memory Map       |                        |                                    |     |  |  |  |

|-------------------------|------------------------|------------------------------------|-----|--|--|--|

| 0x50020000 - 0x5002001F | Peripheral             | 32Byte timer control               | N/A |  |  |  |

| 0x50020020 - 0x50020047 | Flash                  | 40Byte Flash program/erase control | N/A |  |  |  |

| 0x50020048 - 0xDFFFFFFF | N/A                    | Reserved                           | N/A |  |  |  |

| 0xE0000000 - 0xE00FFFFF | Private peripheral bus | ARM peripherals                    | N/A |  |  |  |

| 0xE0100000 - 0xEFFFFFFF | N/A                    | Reserved                           | N/A |  |  |  |

| 0xF0000000 - 0xF0001FFF | System ROM tables      | ARM core IDs                       | N/A |  |  |  |

| 0xF0002000 - 0xFFFFFFFF | N/A                    | Reserved                           | N/A |  |  |  |

## Table 6 Peripheral Fast Access Memory Map

| Peripheral Fast Access Memory Map |            |                               |           |  |

|-----------------------------------|------------|-------------------------------|-----------|--|

| Address                           | Peripheral | Description                   | Reference |  |

| 0x50000000 - 0x50000005           | PMU        | Power management unit control |           |  |

| 0x50000008 - 0x5000000F           | ADC        | ADC control                   |           |  |

| 0x50000010 - 0x50000017           | UART       | UART control                  |           |  |

| 0x5000001C - 0x5000001F           | SPI        | SPI control                   |           |  |

| 0x50000020 - 0x50000031           | RF RX      | RF Receiver control           |           |  |

| 0x50000032 - 0x5000003F           | RF TX      | RF Transmitter control        |           |  |

| 0x50000040 - 0x5000004F           | PWM        | Pulse width modulator control |           |  |

| 0x50000050 - 0x5000005F           | DTT        | Digital Triac Timer control   |           |  |

| 0x50000060 - 0x5000007F           | GPIO       | GPIO Byte control             |           |  |

Table 7 Peripheral Slow Access Memory Map

| Peripheral Slow Access Memory Map |            |                                |           |  |  |  |

|-----------------------------------|------------|--------------------------------|-----------|--|--|--|

| Address                           | Peripheral | Description                    | Reference |  |  |  |

| 0x50010000 - 0x500104FF           | GPIO       | GPIO bit control               |           |  |  |  |

| 0x5000008 - 0x5000000C            | ADC 1      | ADC and miscellaneous control  |           |  |  |  |

| 0x50010004 - 0x50010007           | TX PLL     | RF TX Synthesizer Setting      |           |  |  |  |

| 0x50018004 - 0x50018007           | RX PLL     | RF RX Synthesizer Setting      |           |  |  |  |

| 0x50018008 - 0x5001800B           | ADC 2      | ADC Setting                    |           |  |  |  |

| 0x5000000                         | CLK Source | RC Oscillator and XTAL Setting |           |  |  |  |

| 0x50000060 - 0x5000006A           |            | Port Control                   |           |  |  |  |

## 5.1.2 Timers

Krankl implements three identical timers: Timer0, Timer1 and Timer2. These timers use the system clock as clock source and once activated count up continuously. They start from the value initially loaded into the counting register (32-bit) and, if enabled, generate an interrupt upon rolling over (0xFFFFFFFF  $\rightarrow$  0x00000000).

| TMROREG: 32-bit Timer initial value register |                       |                |                |     |           |     |     |  |

|----------------------------------------------|-----------------------|----------------|----------------|-----|-----------|-----|-----|--|

| TMROREG                                      |                       | 0x50020000     |                |     | 0x0000000 |     |     |  |

| R/W                                          | R/W                   | R/W            | R/W            | R/W | R/W       | R/W | R/W |  |

| Т7                                           | Т6                    | T5             | T4             | Т3  | T2        | T1  | то  |  |

| T15                                          | T14                   | T13            | T12            | T11 | T10       | Т9  | Т8  |  |

| T23                                          | T22                   | T21            | T20            | T19 | T18       | T17 | T16 |  |

| T31                                          | Т30                   | T29            | T28            | T27 | T26       | T25 | T24 |  |

| MSB                                          |                       |                |                |     |           |     | LSB |  |

| Bit31-0 <b>T[3</b>                           | <b>1:0]</b> : Timer R | egister initia | l value regist | er. |           |     |     |  |

## 5.1.2.1 *Timer registers*

| TMR0CTRL: Timer Control |                                        |                            |          |          |          |        |     |  |

|-------------------------|----------------------------------------|----------------------------|----------|----------|----------|--------|-----|--|

| TMR0CTRL                |                                        |                            | 0x500200 | 004      |          | 0x00   |     |  |

| R/W                     | R/W                                    | R/W R/W R/W                |          |          | R/W      | R/W    | R/W |  |

| Reserved                | Reserved                               | Reserved Reserved Reserved |          | Reserved | Reserved | TSTART |     |  |

| MSB                     |                                        |                            |          |          |          |        | LSB |  |

| Bit0 TST                | Bit0 <b>TSTART</b> : Timer enable bit. |                            |          |          |          |        |     |  |

| 0 = Timer not running   |                                        |                            |          |          |          |        |     |  |

| 1 = 1                   | Timer runninរ្                         | 5                          |          |          |          |        |     |  |

| TMR1REG |     |     | 0x500200 | 008 |     | 0x000000 | 000 |

|---------|-----|-----|----------|-----|-----|----------|-----|

| R/W     | R/W | R/W | R/W      | R/W | R/W | R/W      | R/W |

| Τ7      | Т6  | T5  | T4       | Т3  | T2  | T1       | Т0  |

| T15     | T14 | T13 | T12      | T11 | T10 | Т9       | Т8  |

| T23     | T22 | T21 | T20      | T19 | T18 | T17      | T16 |

| T31     | T30 | T29 | T28      | T27 | T26 | T25      | T24 |

| MSB     |     |     |          |     |     |          | LSB |

| TMR1CTRL: Timer Control |               |                                |             |          |          |          |        |  |  |

|-------------------------|---------------|--------------------------------|-------------|----------|----------|----------|--------|--|--|

| TMR1CTRL                |               | 0x5002000C                     |             |          | 0x00     |          |        |  |  |

| R/W                     | R/W           | R/W                            | R/W R/W R/W |          |          | R/W      | R/W    |  |  |

| Reserved                | Reserved      | Reserved                       | Reserved    | Reserved | Reserved | Reserved | TSTART |  |  |

| MSB                     |               | LSB                            |             |          |          |          |        |  |  |

| Bit0 <b>TST</b>         | ART: Timer er | Bit0 TSTART: Timer enable bit. |             |          |          |          |        |  |  |

0 = Timer not running

1 = Timer running

| TMR2REG: 32-bit Timer initial value register |     |     |          |     |           |     |     |

|----------------------------------------------|-----|-----|----------|-----|-----------|-----|-----|

| TMR2REG                                      |     |     | 0x500200 | 010 | 0x0000000 |     |     |

| R/W                                          | R/W | R/W | R/W      | R/W | R/W       | R/W | R/W |

| Τ7                                           | Т6  | T5  | T4       | Т3  | T2        | T1  | то  |

| TMR2REG: 32-bit Timer initial value register |                                                                 |     |     |     |     |     |     |  |

|----------------------------------------------|-----------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|

| T15                                          | T14                                                             | T13 | T12 | T11 | T10 | Т9  | Т8  |  |

| T23                                          | T22                                                             | T21 | T20 | T19 | T18 | T17 | T16 |  |

| T31                                          | Т30                                                             | T29 | T28 | T27 | T26 | T25 | T24 |  |

| MSB LSB                                      |                                                                 |     |     |     |     |     |     |  |

| Bit31-0 <b>T[3</b> :                         | Bit31-0 <b>T[31:0]</b> : Timer Register initial value register. |     |     |     |     |     |     |  |

| TMR2CTRL: Timer Control                                                              |          |             |            |          |          |          |        |  |

|--------------------------------------------------------------------------------------|----------|-------------|------------|----------|----------|----------|--------|--|

| TMR2CTRL                                                                             |          |             | 0x50020014 |          |          | 0x00     |        |  |

| R/W                                                                                  | R/W      | R/W R/W R/W |            |          | R/W      | R/W      | R/W    |  |

| Reserved                                                                             | Reserved | Reserved    | Reserved   | Reserved | Reserved | Reserved | TSTART |  |

| MSB                                                                                  |          |             |            |          |          |          | LSB    |  |

| Bit0 <b>TSTART</b> : Timer enable bit.<br>0 = Timer not running<br>1 = Timer running |          |             |            |          |          |          |        |  |

## 5.1.2.2 Timer Operation

The operation of the timers is quite straightforward: Load the initial counter register, enable the timer and either check (polling mode) the current value of the counter register or enable the interrupt and process it inside the interrupt service routine.

<u>Note</u>: Inside the interrupt the application code must reload the timer counting register.

Code Example1: Enable Timer1 to count from 0xFFFF0000 and to generate interrupt:

```

TMR_Config( 1, TIMERON, 0xFFFF0000); //Enable timer1 to count up from 0xFFFF0000

NVIC_ClearPendingIRQ( TIMER1_IRQn ); //Clear pending interrupt

NVIC_EnableIRQ( TIMER1_IRQn ); //Enable Timer1 interrupt

```

```

void Timer1_Handler( void )

{

*TMR1REG = 0xFFFF0000; //Reload Register

//**** From this point application code inside ISR****

}

```

## 5.1.3 Watch Dog Timer (WDT)

Krankl implements a WDT (Watch Dog Timer) that can operate in one of two basic ways:

- Interrupt Mode: In the event of a WDT rollover an interrupt will be generated.

- Reset Mode: In the event of a WDT rollover the microcontroller will reset.

## 5.1.3.1 WDT Registers

The Watch Dog Timer implements two 32-bit registers:

| WDTCTRL: WDT Control Register. (32-bit) |          |            |              |              |                  |         |       |

|-----------------------------------------|----------|------------|--------------|--------------|------------------|---------|-------|

| WDTCTRL                                 |          | 0x50020018 |              |              | 020018 0x000000x |         |       |

| Reserved                                | Reserved | Reserved   | R/W          | R/W          | R/W              | R/W     | R/W   |

| -                                       | -        | -          | WDTPRES<br>1 | WDTPRES<br>0 | RSTFLAG          | RESETEN | WDTEN |

| -                                       | -        | -          | -            | -            | -                | -       | -     |

| -                                       | -        | -          | -            | -            | -                | -       | -     |

| -                                       | -        | -          | -            | -            | -                | -       | -     |

| MSB                                     |          |            |              |              |                  |         | LSB   |

WDTCTRL: WDT Control Register. (32-bit)

#### Bit4-3 WDTPRES1: WDTPRES0: WDT Prescaler:

$00 = 2^{13}$ /SystemClock

01 = 2<sup>19</sup>/SystemClock

10 = 2<sup>22</sup>/SystemClock

11 = 2<sup>32</sup>/SystemClock

Bit2 **RSTFLAG**: Reset Flag. This flag is set by the system at the initialization if the initialization was

caused by a reset triggered by the WDT. The bit can be de-asserted by the application.

Bit1 **RESETEN**: Reset enable. If enabled a WDT time-out will force the microcontroller to reset. This

bit can be asserted but it cannot be de-asserted.

Bit0 **WDTEN**: WDT enable. This bit can be asserted but it cannot be de-asserted. It means that once

the WDT is enabled it cannot be turned off until a Reset or Power-On Reset occurs.

For instance, a system running from a 30MHz Crystal with WDTPRES[1...0] = 10 will trigger the WDT after approximately 0.14seconds if not cleared properly and in time by the application.

| WDTCLR: WDT Clear Register. (32-bit) |                        |        |        |            |        |        |        |

|--------------------------------------|------------------------|--------|--------|------------|--------|--------|--------|

| WDTCLR                               | R 0x5002001C 0x000000x |        |        | 0x5002001C |        |        | 00x    |

| R/W                                  | R/W                    | R/W    | R/W    | R/W        | R/W    | R/W    | R/W    |

| WCLR7                                | WCLR6                  | WCLR5  | WCLR4  | WCLR3      | WCLR2  | WCLR1  | WCLR0  |

| WCLR15                               | WCLR14                 | WCLR13 | WCLR12 | WCLR11     | WCLR10 | WCLR9  | WCLR8  |

| WCLR23                               | WCLR22                 | WCLR21 | WCLR20 | WCLR19     | WCLR18 | WCLR17 | WCLR16 |

| WCLR31                               | WCLR30                 | WCLR29 | WCLR28 | WCLR27     | WCLR26 | WCLR25 | WCLR24 |

| MSB                                  |                        |        |        |            |        |        | LSB    |

WDTCLR: WDT Clear Register. (32-bit)

Bit31-0 **WCLR[31:0]**: Clear Register. To clear the WDT counting the following words must be written in this

order and without any other instruction between then:

0x3C570001

0x007F4AD6

**Warning:** Programming WDTCLR with other values or in the wrong order will cause the watchdog to throw an interrupt or reset the system.

#### Example Code: Setting and clearing the WDT. (Interrupt mode with a time of 2^22)

```

WDT_Config(WDT_INT, WDT22); //Enable WDT in interrupt mode (2^22 system clock

cycles)

WDT Clear(); //Clear WDT

```

5.1.4 Interrupt Vectors

Krankl implements an interrupt vector defined in the following table:

Table 8 Interrupt Vector table

| Cortex M0 Specific | Exceptions | 5                                                     |                                          |

|--------------------|------------|-------------------------------------------------------|------------------------------------------|

| Name               | Number     | Comments                                              | Required Interrupt Handler<br>(Function) |

| HardFault_IRQn     | -13        | HardFault handler*                                    | HardFault_Handler ( void )               |

| SVCall_IRQn        | -5         | Supervisory call*                                     |                                          |

| PendSV_IRQn        | -2         | Interrupt-driven request<br>for system level service* |                                          |

| SysTick_IRQn       | -1         | SysTick Timer interrupt                               | void SysTick_Handler( void )             |

| Cortex M0 Specifi           | c Exceptions | 5                                                     |                                          |

|-----------------------------|--------------|-------------------------------------------------------|------------------------------------------|

| Name                        | Number       | Comments                                              | Required Interrupt Handler<br>(Function) |

| BrownOut_IRQn               | 0            | Brownout detection<br>interrupt                       | void BrownOut_Handler ( void )           |

| ClkMon_IRQn                 | 1            | Clock monitor interrupt                               | void ClkMon_Handler ( void )             |

| -                           | 2            | Reserved                                              |                                          |

| PIN_IRQn                    | 3            | Pin change interrupt                                  | void PIN_Handler ( void )                |

| RFRE_IRQn                   | 4            | RF: Rising Edge base band signal reception interrupt  | void RFRE_Handler ( void )               |

| RFFE_IRQn                   | 5            | RF: Falling Edge base band signal reception interrupt | void RFFE_Handler ( void )               |

| TX_done_IRQn                | 6            | RF: Burst transmission done interrupt                 | void TX_done_IRQ_Handler ( void )        |

| TX_reload_IRQn              | 7            | RF: Transmission FIFO<br>reload interrupt             | void TX_reload_IRQ_Handler ( void<br>)   |

| UART_IRQn                   | 8            | UART                                                  | void UART_Handler ( void )               |

| -                           | 9            | Reserved                                              | void Default_IRQ_Handler ( void )        |

| SPI_IRQn                    | 10           | SPI                                                   | void SPI_Handler ( void )                |

| -                           | 11           | Reserved                                              | void Default_IRQ_Handler ( void )        |

| RFMSG_IRQn                  | 12           | RF: Message received<br>interrupt                     | void RFMSG_Handler ( void )              |

| IRQ13_IRQn to<br>IRQ15_IRQn | 13-15        | Reserved                                              | void Default_IRQ_Handler( void )         |

| TIMER0_IRQn                 | 16           | Timer0 interrupt                                      | void Timer0_Handler ( void )             |

| TIMER1_IRQn                 | 17           | Timer1 interrupt                                      | void Timer1_Handler ( void )             |

| TIMER2_IRQn   | 18 | Timer2 interrupt         | void Timer2_Handler ( void )   |

|---------------|----|--------------------------|--------------------------------|

| WATCHDOG_IRQn | 19 | Watchdog timer interrupt | void Watchdog_Handler ( void ) |

\*Note: For more information see Cortex-MO Devices – Generic Users Guide (ARM DUI 0497A (ID112109)) at: http://infocenter.arm.com/help/topic/com.arm.doc.dui0497a/DUI0497A cortex m0 r0p0 generic ug.pdf

# 5.2 RF Receiver Subsystem

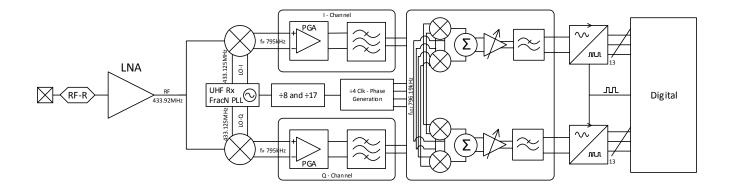

Krankl implements a programmable ISM (Industrial, scientific and medical band, 300-450MHz) OOK (on-off keying) low-IF receiver. The local oscillator is generated using a fully integrated fractional-N PLL referenced to an external crystal reference. The received data is digitized using analog to digital converters before being processed by an autonomous digital section.

The receiver uses Weaver architecture for image rejection, primarily to avoid noise imaging. After amplification through an LNA, a RF mixer is used to generate I/Q signals at the IF frequency of 795KHz, where it is filtered to ~500KHz bandwidth. After the second frequency conversion, the I and Q signals are filtered to ~150kHz bandwidth. The wide bandwidth relative to the data symbol rate is necessary to accommodate manufacturing variation in the transmit and receive frequency references.

The frequency generation for the local oscillators is accomplished using a PLL locked to the crystal frequency. The VCO is a low current quadrature ring oscillator. It is expected that 30MHz crystal in combination with a divide by 8 prescaler stage will be utilized for frequency reference. FXO is equivalent to 3.75MHz. In the default frequency plan, the first LO is generated from 115.5\*fXO = 433.125MHz using the PLL in frac-N mode. The second LO is generated by dividing the first LO, first by a high speed divide-by-eight prescalar, followed by a programmable divider and a quadrature divideby-four. The default frequency plan uses divide by 17 for the programmable part, for a second LO of 796.2kHz. Therefore the overall division ratio for the LO2 signals equal 544 (8x17x4), to be verified in the frequency table below.

| _ | Table  | 9     |       |        |        |       |         |         |       |        |            |

|---|--------|-------|-------|--------|--------|-------|---------|---------|-------|--------|------------|

|   | F_RX   | F_REF | F_EN  | NX     | NF     | HISD  | DIV_LO2 | F_LO1   | F_IF  | F_LO2  | Freq_error |

|   | MHz    | MHz   | {0,1} | {1255} | {0255} | {0,1} | {03}    | MHz     | kHz   | kHz    | kHz        |

|   | 433.92 | 3.75  | 1     | 115    | 128    | 1     | 1       | 433.125 | 795.0 | 796.19 | -1.186     |

Due to the slight difference between the LO and IF frequencies, there is a 1.2kHz frequency offset in the baseband data, which appears as a slight additional transmit frequency error to the decoder. For other crystal frequencies, different settings will need to be programmed for the PLL and divider as described below.

After analog filtering, the baseband signal is then digitized at 298kS/s using a 12bit ADC. The digitized signal is dc-offset corrected and AM detected using a CORDIC to produce an AM baseband signal, which is filtered and decimated to an approximately 5kHz bandwidth with 18.6kS/s data rate.

Data is digitally extracted from filtered baseband signal using a digital bit slicer. An integrated decoder may be utilized to decode 1/3-2/3 duty-cycle encoded data. Decoded bits are stored in a bit buffer with capability to store messages as long as 80 bits. Once an entire valid message is stored in the RF bit buffer, an interrupt is generated. The receiver then enters an armed state, but with decoder inactive until the microcontroller re-enables the receiver to receive subsequent messages. The microcontroller should read any data from the bit buffer before re-enabling or else it will be lost.

Alternatively, if an application requires a coding scheme other than 1/3-2/3 coding, the slicer digital output may be made available in real time for the micro to decode the signal by software. The raw signal is guaranteed glitch-free, allowing a simple decode.

The receiver can be run in an autonomous "sniffing" mode with, for example, a 5% on-time duty cycle, in order to save power. Whether in sleep mode or not, intervention by the microcontroller is only required upon reception of an entire message with valid number of bits. The micro can therefore be asleep during normal RF reception, and only needs be awoken by interrupt after an entire message arrives, allowing significant power savings.

Additionally, functional control such as enabling and disabling the receiver, and the received bits are controllable through registers. The register section describes the functions of various registers related to the receiver. All control registers preset when power-on reset or software reset is asserted.

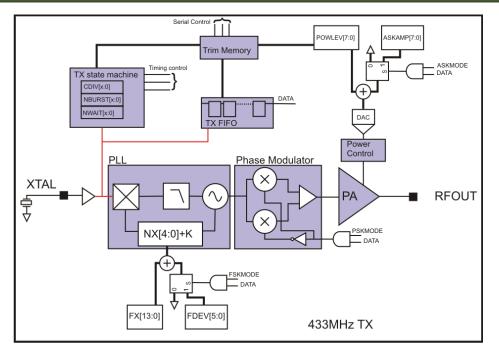

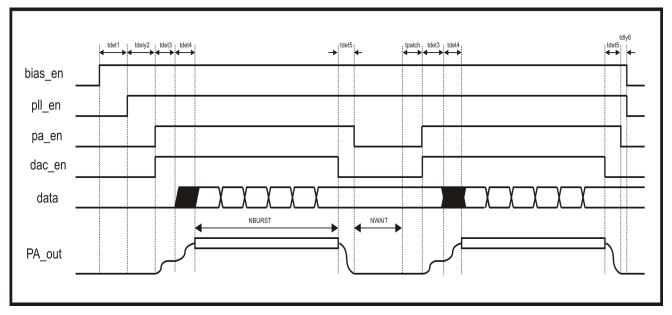

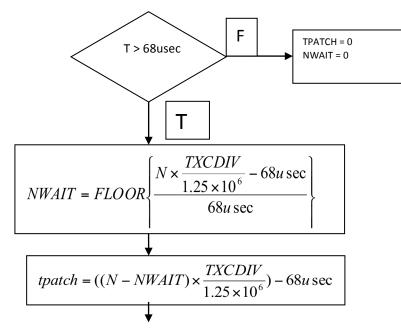

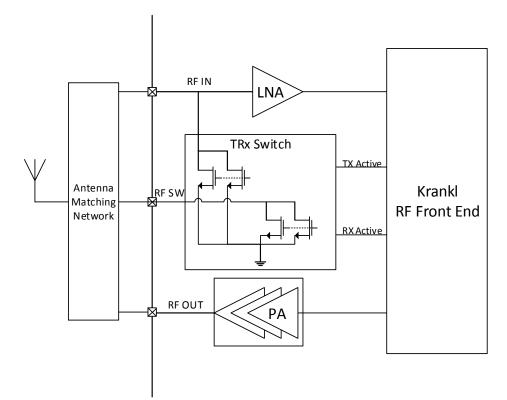

Figure 2 RF Receiver subsystem

## 5.2.1 **RF Receiver Registers**

| <b>RF Receiver Reg</b> | ister Map     |              |                                                                        |

|------------------------|---------------|--------------|------------------------------------------------------------------------|

| Address                | Register Name | Field Name   | Description                                                            |

| 0x50000020             | RF_Buff0-F    | RXDATA 0-127 | RF Buffer Registers containing received bits.                          |

| 0x50000030             | RF_NUMB       | RFNUMB0-7    | Returns the number of bits contained in the bit buffer                 |

| 0x50000031             | RF_STATUS     | RF_SLEEP     | RF sleep mode indicator                                                |

|                        |               | SLC_OUT      | Slicer output                                                          |

|                        |               | DCDMD0       | Determines whether state machine transitions on edge or level          |

|                        |               | DCDMD1       | Determines what to do if there is a overly-long non-guard band element |

|                        |               | ADC_FLG      | Overflow indicator                                                     |

|                        |               | MSG_RDY      | Message ready indicator                                                |

|                        |               | SNF_EN       | Enables sniff/sleep mode in the receiver                               |

|                        |               | RF_EN        | Enables RF blocks                                                      |

| 0x50011000             | RF_NBMIN      | Low_BPS      | Indication to interpret all bit timings as 2X (slow transmitter)       |

|                        |               | NBMIN[6:0]   | Minimum number of bits for a valid transaction                         |

| 0x50011001             | RF_AGCCTRL    | AGC_EN       | Automatic gain control enable                                          |

|                        |               | AGCTRM[6:0]  | Controls gain of analog blocks                                         |

| 0x50011002             | RF_SLCCTRL    | ALPHA[1:0]   | Controls decay time of slicer level                                    |

|                        |               | BETA[1:0]    | Controls attack time of slicer level                                   |

|                        |               | FTIME[1:0]   | Controls the time to allow the slicer to fast bias                     |

|                        |               | DR_SYM[1:0]  | Sets post-CORDIC decimation rate                                       |

| 0x50011003             | RF_SYSTIME    | PLLTIME[1:0] | Controls time to wait for PLL to bias                                  |

|              |             | SLEEPTIME[2:0] | Controls sleep time between sniff cycles                                                                                                   |

|--------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|              |             | WAKETIME[2:0]  | Controls the time to stay awake after seeing a valid guard band                                                                            |

| 0x50011004/5 | RF_DCDTIME  | MIN_GB[5:0]    | Minimum number of additional<br>samples after passing MIN_TE and<br>MAX_TE for a low element to be<br>considered a valid guard band length |

|              |             | MAX_TE[5:0]    | Maximum number of additional<br>samples after passing MIN_TE for an<br>edged to be considered short<br>enough to be valid                  |

|              |             | MIN_TE[3:0]    | Minimum number of samples for a valid element time                                                                                         |

| 0x50011006   | RF_SNIFMODE | RT_SEL[1:0]    | Selects a source for real time output                                                                                                      |