# iND80001 "Lodestar"

indie's ultra-integrated USB 3.1 type-C cable marker (E-marker) chip.

12/10/2015

**Preliminary Data sheet**

# 1.0 TABLE OF CONTENT

| 1.0  | TABLE OF CONTENT                 | 2    |

|------|----------------------------------|------|

| 2.0  | LIST OF TABLES                   | 3    |

| 3.0  | LIST OF FIGURES                  | 3    |

| 4.0  | GENERAL DESCRIPTION              | 4    |

| 4.1  | Key Features                     | 4    |

| 4.2  | Main Functions & System overview | 5    |

| 4.3  | Application Diagram              | 6    |

| 5.0  | ELECTRICAL CHARACTERISTICS       | 7    |

| 5.1  | Absolute Maximum Ratings         | 7    |

| 5.2  | Operating conditions             | 7    |

| 6.0  | PROGRAMMING                      | 9    |

| 6.1  | Messages Supported               | 9    |

| 6.2  | VDM Command Overview             | 9    |

| 6.3  | Programming                      | . 10 |

| 7.0  | FUSE MAP                         | 11   |

| 7.1  | ID VDM                           | .11  |

| 7.2  | Cert Stat VDM                    |      |

| 7.3  | Product VDO                      |      |

| 7.4  | Cable VDO                        |      |

| 7.5  | Analog Trimming Fuses            |      |

| 8.0  | PACKAGING OPTIONS                |      |

| 8.1  | WLCSP-4 Package                  |      |

| 8.2  | DFN-6 Package                    | . 16 |

| 9.0  | REFERENCES                       | 17   |

| 10.0 | REVISION HISTORY                 | 17   |

| 11.0 | ORDERING INFORMATION             | 17   |

| 12 N | CONTACTS                         | 12   |

# 2.0 LIST OF TABLES

| Table 1  | Absolute Maximum Ratings                       | 7  |

|----------|------------------------------------------------|----|

| Table 2  | Operating Conditions                           | 8  |

| Table 3  | Type-C message                                 | 9  |

| Table 4  | VDM Command Overview                           | 9  |

| Table 5  | Programming Commands                           | 10 |

| Table 6  | ID VDM                                         | 11 |

| Table 7  | Cert Stat VDM                                  | 11 |

| Table 8  | Product VDO                                    | 12 |

| Table 9  | Cable VDO                                      | 12 |

| Table 10 | Analog Trimming Fuses                          | 13 |

| Table 11 | WLCSP Pin assignments                          | 15 |

| Table 12 | DFN-6 Pin Assignments                          | 16 |

| Table 13 | Revision History                               | 17 |

| Table 14 | Ordering information                           | 17 |

| 3.0 L    | IST OF FIGURES                                 |    |

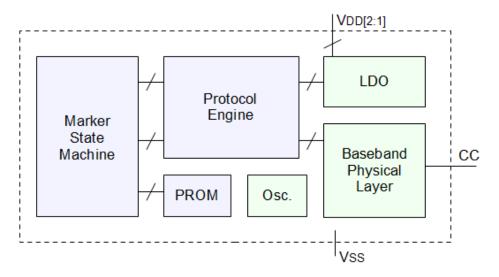

| Figure 1 | iND80001 Block Diagram                         | 5  |

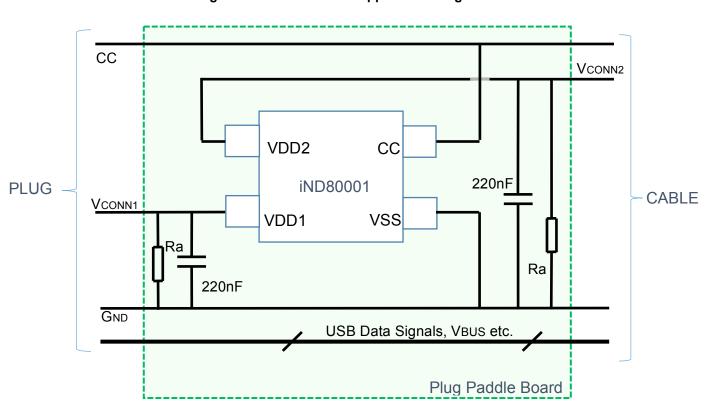

| Figure 2 | iND80001 Application Diagram                   | 6  |

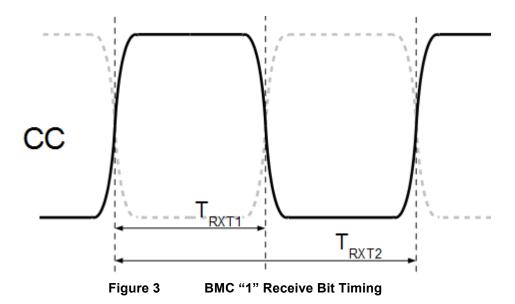

| Figure 3 | BMC "1" Receive Bit Timing                     | 7  |

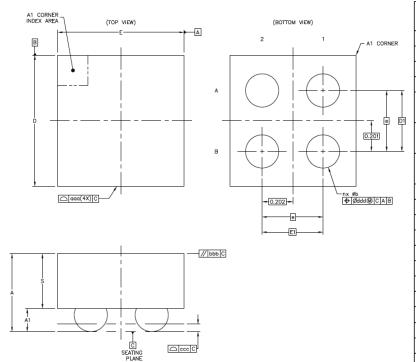

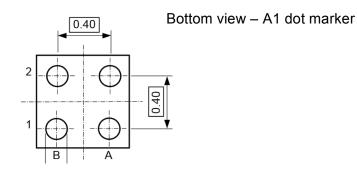

| Figure 4 | WLCSP 4 package drawing                        | 14 |

| Figure 5 | A1 marker                                      | 14 |

| Figure 6 | WLCSP 4 marker position in Tape an Reel        | 15 |

| Figure 7 | DFN-6 2x2 package TOP View and Bonding Diagram | 16 |

# 4.0 GENERAL DESCRIPTION

The iND80001 is a complete low cost, single chip cable marker for USB PD Type-C (baseband) cables. With low silicon area and just 4 IOs the device is designed exclusively for very high volume Type-C cables with basic marker requirements.

#### 4.1 KEY FEATURES

- USB PD 2.0 compliant.

- USB Type-C 1.0 compliant

- Single chip solution.

- 4 pin package.

- PROM programmed through vendor message protocol.

- Based on Obsidian Technology's mature PD technology.

- Integrated PROM enables customized response to a wide range of vendor requirements.

- Power <5mW. Enabled by CC data activity. I.e. very low duty cycle.</li>

- Programming can be done after assembly into the cable.

- Fuse lock function.

- Supports low cost 4 layer PCB assembly.

- Supported with module level test program.

- Package options: WLCSP4, DFN6

- CC high impedance when powered down.

- IEC61000-4-2 4kV ESD protection

#### 4.2 Main Functions & System overview

#### Physical Layer.

Based on Obsidian's OTC9107 port chip physical layer, this provides CC line driving and reception

without external components. It includes data slicer, activity detection, voltage level detection, and

slew rate controlled driver.

#### LDO.

Provides bandgap, and internal voltage regulation for the logic the physical layers. Power diodes

also provide the required power isolation between two possible power sources (one at each end of

the cable).

#### Oscillator.

• A low temperature drift 12MHz oscillator provides logic clocking when required. The provided test program automatically trims the oscillator during test for an overall frequency accuracy of ±5%.

#### **Protocol Engine.**

Implements the low level protocol and logic PHY functions required by the standard, such as CRC generation and testing, 4b5b coding, BMC coding, clock recovery, and SERDES.

#### Marker State Machine.

Provides the subset of device functions required to recognize vendor messages and return responses based on PROM data.

**Programmed response** will respond with Cert-Stat VDO and Cable-VDO with all relevant fields programmable.

#### Programming Board is available.

**Supporting Software** in C form is available for rapid implementation of production test.

Figure 1 iND80001 Block Diagram

#### 4.3 APPLICATION DIAGRAM

The iND8001 is a single chip marker that requires only the VDD and VSS pins to be decoupled by external capacitors. 16V 220nF ceramic types are recommended.

The applications diagram shows a typical arrangement for single chip per cable. However, it is also possible to fit the plug at both ends with an identical chip, and avoid needing to provide a VCONN conductor through the cable. This is more cost effective for long cables.

Figure 2 iND80001 Application Diagram

# 5.0 ELECTRICAL CHARACTERISTICS

#### 5.1 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Table 1 Absolute Maximum Ratings**

| Parameter                                         | Rating        |

|---------------------------------------------------|---------------|

| Maximum voltage range on VDD1, VDD2, or CC Vs VSS | -0.75 - 6V    |

| Junction temperature range                        | -65°C – 150°C |

| Storage temperature range                         | -65°C – 150°C |

| CC pin short circuit time                         | Indefinite    |

#### 5.2 OPERATING CONDITIONS

#### **Table 2 Operating Conditions**

Measured at  $T_A = 25$ °C,  $V_{DD} = 5V$  unless otherwise started.

| Parameter                                                         | Condition                                                                   | Min | Тур  | Max  | Units |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|------|------|-------|

| Operating Voltage V <sub>O</sub>                                  | Max(V <sub>DD1</sub> ,V <sub>DD2</sub> )                                    | 4.5 | 5    | 5.5  | V     |

| Operating Temperature T <sub>O</sub>                              |                                                                             | -40 |      | 125  | °C    |

| Idle current I <sub>IDL</sub>                                     | Current into $V_{DD1}$ + $V_{DD2}$ with no CC bus activity                  |     | 55   |      | μA    |

| Transmit current I <sub>TX</sub>                                  | Mean current into V <sub>DD1</sub> + V <sub>DD2</sub> during transmit       |     | 900  |      | μA    |

| Receive current I <sub>RX</sub>                                   | Mean current into V <sub>DD1</sub> + V <sub>DD2</sub> during packet receive |     | 150  |      | μA    |

| Receive lock time T <sub>RXL</sub>                                | First CC edge to good received edge                                         |     |      | 18   | μS    |

| Receive BMC "1" centre bit edge timing window $T_{\text{RXT1}}$ . | CC 1 <sup>ST</sup> UI edge to "1" edge if present                           | 1.2 |      | 2.03 | μS    |

| Receive BMC end of bit window T <sub>RXT2</sub> .                 | CC 1 <sup>ST</sup> UI edge to end of bit edge                               | 2.6 |      | 4.0  | μS    |

| Clock off time T <sub>CKO</sub>                                   | Last CC edge to clock off                                                   | 50  |      | 200  | μS    |

| Transmit drive high voltage V <sub>TH</sub>                       | CC load 0 – 1.2nF, or open transmission line over T <sub>RNG</sub>          | 1.0 | 1.1  | 1.2  | V     |

| Transmit drive low voltage V <sub>TL</sub>                        | CC load 0 – 1.2nF, or open transmission line over T <sub>RNG</sub>          | 0   |      | 0.1  | V     |

| Transmit driver rise/fall T <sub>TRF</sub> (Trimmed during test)  | CC load 0 – 1.2nF, or open transmission line                                | 200 | 300  | 500  | nS    |

| Transmitter Unit Interval Time $T_{TUI}$ (Trimmed during test)    | CC pin, typical load                                                        | 1.5 | 1.66 | 1.83 | μS    |

| Oscillator temperature drift                                      | -40°C – 125°C                                                               |     |      | 2    | %     |

| CC pin impedance Z <sub>CC</sub>                                  | 0V < V <sub>CC</sub> < 5V                                                   |     | 1    |      | ΜΩ    |

# 6.0 PROGRAMMING

#### 6.1 Messages Supported

The iND80001 supports baseband messages required for basic Type-C cable markers as follows:

Table 3 Type-C message

| PD Message type     | Code      | Action                                                                                            |

|---------------------|-----------|---------------------------------------------------------------------------------------------------|

| Soft Reset          | 1101      | Normal Soft Reset, reset ID-counter and discard any message waiting to be sent.                   |

| BIST                | 0011/0101 | Can turn on BIST mode 2.                                                                          |

| Vendor Defined      | 1111      | See table below.                                                                                  |

| Private Programming | 0000      | Intended to program the chip before being taken into use. See Table 5 Programming Commands below. |

A GoodCRC message will not be answered.

Any message except those in the table above will be ignored after being acknowledged.

#### 6.2 VDM COMMAND OVERVIEW

**Table 4 VDM Command Overview**

| Structured VDM<br>Command | Command | Action                  |

|---------------------------|---------|-------------------------|

| Any unstructured VDM      | NA      | Ignored                 |

| Discover Identity         | 1       | ACK with response       |

| Discover SVIDs            | 2       | NAK                     |

| Discover Modes            | 3       | NAK                     |

| Enter Mode                | 4       | NAK                     |

| Exit Mode                 | 5       | ACK no further response |

| Attention                 | 6       | NAK                     |

| Any other code            |         | NAK                     |

#### 6.3 PROGRAMMING

- Programming is done by sending messages with header message code "0000". This is a reserved code. Once programming is finished and the locking fuse has been blown, the command will be completely ignored.

- Each programming command carries a PDO of 32 bits as data. This data block is split into 8 bits of command (8 MSB's) and 24 bits of data (24 LSB's). The following table shows how the commands are structured.

#### Table 5 Programming Commands

| Name  | bit 31-28 | bit 27-24                         | Action                                                                                                          |

|-------|-----------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Test  | 0x0       | Tst[3:0]                          | For device test only. Note transition of txt[0] to 1 initiates a power on burst. Other combinations are static  |

| Сору  | 0x1       | Address of fuse group (see below) | Copy data from message b23-0 to the group address indicated in bits 27-24to the address indicated in bits 27-24 |

| Burn  | 0x2       | х                                 | Start programming of fuses                                                                                      |

| Arm   | 0x4       | Х                                 | Arm the final fuse                                                                                              |

| Final | 0x8       | х                                 | Program final fuse                                                                                              |

Any combination of bits 31-28 not mentioned in table is a NOP.

Programming of the content will follow this sequence:

| • | Copy (23-0)    | address 0 |

|---|----------------|-----------|

| • | Copy (47-24)   | address 1 |

| • | Copy (71-48)   | address 2 |

| • | Copy (95-72)   | address 3 |

| • | Copy (119-96)  | address 4 |

| • | Copy (126-120) | address 5 |

<at this time the responses from the Marker chip will be the same as after burning>

- Burn

- Wait 100 mS

- Arm

- Final

<Note: The Arm and Final must follow directly any other message to command "0000" will disarm>

# 7.0 FUSE MAP

In the tables below each bit in the VDOs are mapped to corresponding fuses.

## 7.1 ID VDM

#### Table 6 ID VDM

| Bit(s) | Description                                                                                                                                  | Fuses   | Coding                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|

| 31     | Data Capable as USB Host: - Shall be set to one if the product is capable of enumerating USB Devices Shall be set to zero otherwise.         | 105     | 0                       |

| 30     | Data Capable as a USB Device: - Shall be set to one if the product is capable of enumerating as a USB Device Shall be set to zero otherwise. | 104     | 0                       |

| 29:27  | Product Type: - 011b – Passive Cable - 100b – Active Cable                                                                                   | 103:101 | 0 -> "011"<br>1-> "100" |

| 26     | Modal Operation Supported:- Shall be set to one if the product supports Modal Operation Shall be set to zero otherwise.                      | 100     | 0                       |

| 25:16  | Reserved. Set to zero.                                                                                                                       |         | _                       |

| 15:0   | 16-bit unsigned integer. USB Vendor ID.                                                                                                      | 99:84   | TID                     |

#### 7.2 CERT STAT VDM

#### **Table 7 Cert Stat VDM**

| Bit(s) | Description                     | Fuses | Coding |

|--------|---------------------------------|-------|--------|

| 31:20  | Reserved. Shall be set to zero. |       |        |

| 15:0   | 20-bit unsigned integer.        | 83:64 | TID    |

#### 7.3 PRODUCT VDO

#### **Table 8 Product VDO**

| Bit(s) | Description    | Fuses |

|--------|----------------|-------|

| 31:16  | USB Product ID | 63:48 |

| 15:0   | bcdDevice      | 47:32 |

## 7.4 CABLE VDO

#### Table 9 Cable VDO

| Bit(s) | Description                                                                                                                                     | Fuse(s) |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 31:28  | Cable HW Version                                                                                                                                | 31:28   |

| 27:24  | Cable Firmware Version                                                                                                                          | 27:24   |

| 23:20  | Reserved                                                                                                                                        | 23:20   |

| 19:18  | Type-C to Type-A, B, or C                                                                                                                       | 19:18   |

| 17     | Type-C to Plug/Receptacle                                                                                                                       | 17      |

| 16:13  | Cable Latency                                                                                                                                   | 16:13   |

| 12:11  | Cable Termination Type                                                                                                                          | 12:11   |

| 10     | SSTX1 Directionality Support                                                                                                                    | 10      |

| 9      | SSTX2 Directionality Support                                                                                                                    | 9       |

| 8      | SSRX1 Directionality Support                                                                                                                    | 8       |

| 7      | SSRX2 Directionality Support                                                                                                                    | 7       |

| 6:5    | VBUS Current Handling Capability                                                                                                                | 6:5     |

| 4      | VBUS through cable                                                                                                                              | 4       |

| 3      | SOP" controller present?                                                                                                                        | 3       |

| 2:0    | USB Superspeed Signaling Support: 00 -> "000" - USB 2.0 only 01 -> "001" - USB 3.1 Gen 1 10 -> "010" - USB 3.1 Gen 1 & 2 11 -> "011" - Reserved | 2:0     |

# 7.5 ANALOG TRIMMING FUSES

Table 10 Analog Trimming Fuses

| Name        | Description                            | Fuse(s) |  |

|-------------|----------------------------------------|---------|--|

| ftrim[3:0]  | Trim for on chip oscillator (inverted) | 115:112 |  |

| range       | Range bit for oscillator. aka ftrim[4] | 116     |  |

| bgvtrm[2:0] | Bandgap voltage trim                   | 119:117 |  |

| bgitrm[1:0] | bandgap IPTAT current output trim      | 121:120 |  |

| itrim[1:0]  | Current reference trim                 | 123:122 |  |

| spare       | Unused fuse                            | 124     |  |

| rtrim[1:0]  | Trim for driver rise and fall times    | 126:125 |  |

# 8.0 PACKAGING OPTIONS

#### 8.1 WLCSP-4 PACKAGE

The WLCSP-4 package option has 4 balls with 400μ pitch. Package size is 800μ × 800μ.

WLCCSP version does not require a CAP pin. Balls are shown on the reverse (down) side of the package. Drawing not to scale.

|                            |     | SYMBOL | COMMON | DIM   | ENSIONS |

|----------------------------|-----|--------|--------|-------|---------|

| TOTAL THICKNESS            | Α   | 0.512  | ±      | 0.055 |         |

| WAFER THICKNESS            |     | S      | 0.36   | ±     | 0.025   |

| STAND OFF                  |     | A1     | 0.122  | ~     | 0.182   |

| FILM THICKNESS             |     | A2     |        | ±     |         |

| BODY SIZE                  | Х   | E      | 0.83   |       |         |

| BODT SIZE                  | Y   | D      | 0.861  |       | 1       |

| BALL/BUMP PITCH            | Х   | SE     |        | -     | BSC     |

| BALL/BOMP FITCH            | Y   | SD     |        | -     | BSC     |

| EDGE BALL CENTER TO CENTER | Х   | E1     | 0.4    |       | BSC     |

| EDGE BALL CENTER TO CENTER | Y   | D1     | 0.4    |       | BSC     |

| PITCH                      |     | е      | 0.4 BS |       | BSC     |

| BALL DIAMETER (SIZE)       |     |        | 0.2    |       |         |

| BALL/BUMP WIDTH            | ь   | 0.188  | ~      | 0.248 |         |

| BALL/BUMP COUNT            | n   | 4      |        |       |         |

| PACKAGE EDGE TOLERANCE     | 000 | 0.03   |        |       |         |

| WAFER FLATNESS             | bbb | 0.06   |        |       |         |

| COPLANARITY                | ccc | 0.05   |        |       |         |

| BALL/BUMP OFFSET (PACKAGE) | ddd | 0.015  |        |       |         |

| BALL ALLOY                 |     |        | SAC405 |       |         |

|                            |     |        |        |       |         |

|                            |     |        |        |       |         |

|                            |     |        |        |       |         |

Figure 4 WLCSP 4 package drawing

- Font size tolerance: (+/- 0.05mm)

- Marking shift tolerance: (+/- 0.15mm)

# Example Marking format 0.20 Unit : mm

Figure 5 A1 marker

#### Notes:

- Index is a dot marker referring to pin A1 position

- There are no other marking on the package top

Table 11 WLCSP Pin assignments

| Pin | Name               |

|-----|--------------------|

| A1  | VDD1 / VCONN 1 (0) |

| B1  | VSS                |

| A2  | VDD2 / VCONN 2 (1) |

| B2  | СС                 |

#### Note:

Power supply VDD1 and VDD2 being interchangeable, they can be referred to as VCONN (1, and 2 - or possibly 0 and 1)

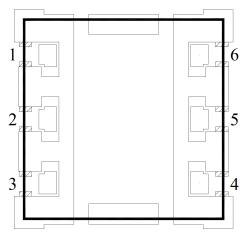

Figure 6 WLCSP 4 marker position in Tape an Reel

# 8.2 DFN-6 PACKAGE

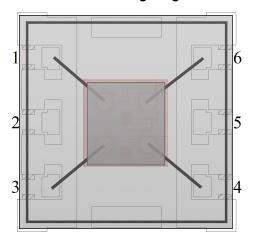

Indie can also support a DFN 6-lead package in a small 2x2 form factor. The DFN-6 package drawing and dimensions are shown on Figure 7.

Figure 7 DFN-6 2x2 package TOP View and Bonding Diagram

| ALL LEADS AND PADS MUST BE WIRED EXCEPT 🏮 OR X |  |                        |  |             |               |    |

|------------------------------------------------|--|------------------------|--|-------------|---------------|----|

| PLEASE INDICATE THE DIE MARK OR LOGO LOCATION  |  | DIE ID                 |  | PART NUMBER | 0006SN001F05K |    |

| CUSTOMER                                       |  | WIRE AMOUNT            |  | PKG TYPE    | SON           |    |

| CUSTOMER B/D NO.                               |  | PAD TO PAD WIRE AMOUNT |  | LEAD COUNT  | 6             |    |

| MIN.PAD PITCH (mm)                             |  | TOTAL WIRE LENGTH (mm) |  | LEAD PITCH  | 0.65          | mm |

| MIN.PAD OPENING (mm)                           |  | MAX. WIRE LENGTH (mm)  |  | BODY SIZE   | 2X2           | mm |

| WIRE MATERIAL                                  |  | MIN. WIRE LENGTH (mm)  |  | FLAG SIZE   | 1X1.7         | mm |

| WIRE DIA. (mil)                                |  | SHEET                  |  | PLATING     | DOUBLE RING   |    |

Table 12 DFN-6 Pin Assignments

| Pin         | Name |

|-------------|------|

| 1           | VDD1 |

| 3           | СС   |

| 4           | VSS  |

| 6           | VDD2 |

| Other (2,5) | NC   |

Notes: Pin 1 marking and labeling information to come

# 9.0 REFERENCES

[1] USB 3.1 Type C specification, <a href="http://www.usb.org/developers/docs/">http://www.usb.org/developers/docs/</a>

Available soon:

- [2] indie e-marker reference design

- [3] indie cable test board specification and programming information

# **10.0 REVISION HISTORY**

**Table 13 Revision History**

| Rev# | Date       | Action                             | Ву    |

|------|------------|------------------------------------|-------|

| 1.0  |            | Original Obsidian spec 1.0         |       |

| 1.0  | 6/18/2015  | indie format and part number       | CR    |

| 2.0  | 12/07/2015 | Update on diagram, BoM and package | RH/CR |

| 2.1  | 12/10/2015 | Update contacts information        | VW    |

# 11.0 ORDERING INFORMATION

Table 14 Ordering information

| Order code     | Description                        |

|----------------|------------------------------------|

| iND80001-c1    | USB Cable Marker in WCSP-4 package |

| iND80001-d1    | USB Cable Marker in DFN-6 package  |

| iND80001EVK_C1 | Cable programming board [3]        |

| iND80001SUP_C1 | WCSP paddle reference design [2]   |

# 12.0 CONTACTS

#### **United States**

32 Journey Aliso Viejo, California 92656, USA Tel: +1 949-608-0854 sales@indiesemi.com

#### China

Rm.7B.Flat A, YangGuangHuaYi Building, No.3003, Nanhai Ave Nanshan District, ShenZhen, China Tel: +86 18665822385 <u>danielzdz@indiesemi.com</u> kevin@hkkeysida.com

#### **Scotland**

5th Floor, The Auction House, 63a George Street Edinburgh EH2 2JG Tel: +44 131 718 6378

http://www.indiesemi.com/

# **Important Notice**

indie semiconductor reserves the right to make changes, corrections, enhancements, modifications, and improvements to indie semiconductor products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on indie semiconductor products before placing orders. indie semiconductor products are sold pursuant to indie semiconductor's terms and conditions of sale in place at the time of order acknowledgement. Purchasers are solely responsible for the choice, selection, and use of indie semiconductor products and services described herein. indie semiconductor assumes no liability for the choice, selection, application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by indie semiconductor by this document.

The materials, products and information are provided "as is" without warranty of any kind, whether express, implied, statutory, or otherwise, including fitness for a particular purpose or use, merchantability, performance, quality or non-infringement of any intellectual property right. Indie semiconductor does not warrant the accuracy or completeness of the information, text, graphics or other items contained herein. indie semiconductor shall not be liable for any damages, including but not limited to any special, indirect, incidental, statutory, or consequential damages, including without limitation, lost of revenues or lost profits that may result from the use of the materials or information, whether or not the recipient of material has been advised of the possibility of such damage.

Unless expressly approved in writing by two authorized indie semiconductor representatives, indie semiconductor products are not designed, intended, warranted, or authorized for use as components in military, space, or aircraft, in systems intended to support or sustain life, or for any other application in which the failure or malfunction of the indie semiconductor product may result in personal injury, death, or severe property or environmental damage.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015, indie semiconductor, all Rights Reserved